Library of Connection Elements ABB Procontic T200

ABB Procontic Programming System

907 PC 332 Programming and Test Software

ABB Schaltund Steuerungstechnik

## Note

The connection elements from the block library expansions 907 PB 360, PB 361 and PB 362 have been integrated into the programming system 907 PC 332.

This connection elements are described in volume 8.

| CE name                                                                                     | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page                                                                                                                                                                                                           | from CE library                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR IDLB IDSB PID-PARA PID-RUN PID-VERW UD_SEND UD_EMPF UD_ANZ                              | Store absolute address Read indirect, bit Write indirect, bit Operate controller Control one cycle Initialize, manage controller Function block for the timer module 07 UD 60 Function block for the timer module 07 UD 60 Function block for the timer module 07 UD 60                                                                                                                                                                                                 | . 2 Vol. 8<br>. 3 Vol. 8<br>. 4 Vol. 8<br>. 6 Vol. 8<br>. 7 Vol. 8<br>. 10 Vol. 8                                                                                                                              | <ul> <li>907 PB 361/362</li> <li>907 PB 361/362</li> <li>907 PB 361</li> <li>907 PB 361</li> <li>907 PB 361</li> <li>907 PB 362</li> <li>907 PB 362</li> </ul>                                                               |

| AMELD BMELD COPY FIFOB FIFOW FKG KT_DRU KT_INI KT_RD KT_WR KT_ZUST LIFO LIZU PI PO_RD PO_WR | Change annunciator, word Change annunciator, bit Copy a memory area FIFO, bit FOFO, word Function generator Output of a text page with variables (07 KT 60) Initialization of text processor 07 KT 60 Block for general text input 07 KT 60 Block for general text output 07 KT 60 Block for interrogating 07 KT 60 condition register LIFO, word List allocator Proportional—integral controller Read communication module 07 PO 60 Write communication block 07 PO 60 | . 19 Vol. 8<br>. 21 Vol. 8<br>. 23 Vol. 8<br>. 24 Vol. 8<br>. 26 Vol. 8<br>. 28 Vol. 8<br>. 30 Vol. 8<br>. 33 Vol. 8<br>. 35 Vol. 8<br>. 38 Vol. 8<br>. 41 Vol. 8<br>. 44 Vol. 8<br>. 46 Vol. 8<br>. 48 Vol. 8 | . 907 PB 360<br>. 907 PB 360<br>. 907 PB 360<br>. 907 PB 360<br>. 907 PB 361<br>. 907 PB 362<br>. 907 PB 360<br>. 907 PB 360<br>. 907 PB 361<br>. 907 PB 361 |

7

## Finding connection elements

In the currently available connection element library, the connection elements are sorted in two different orders. They are sorted:

- 1. in function groups

- 2. alphabetically.

#### Note:

In case of older central units (R101, R201), the processing times of connection elements are 16 % slower than those of central units R302.

0 - 1

## ABB Procontic T 200 functions, arranged according to function groups

The following overview summarizes the connection elements in function groups. You will find a detailed description starting with the stated page.

| Call name in FBD/LD      | Connection element            | Page in CE-library                    |

|--------------------------|-------------------------------|---------------------------------------|

| Binary functions         |                               | · · · · · · · · · · · · · · · · · · · |

| &                        | AND                           | 7                                     |

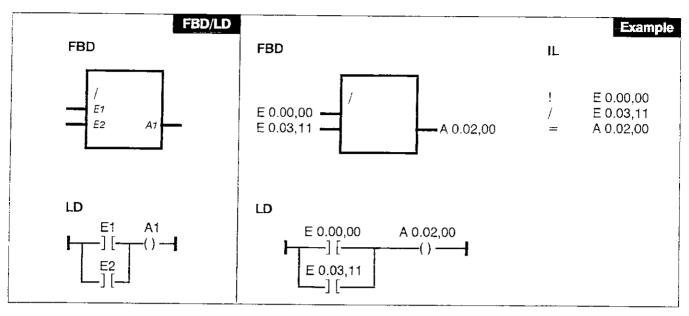

| 1                        | LOGIC OR, BINARY              | 15                                    |

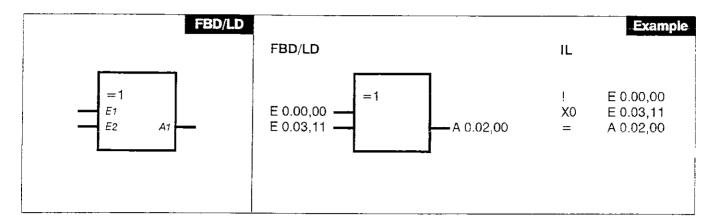

| =1                       | EXCLUSIVE OR, BINARY          | 26                                    |

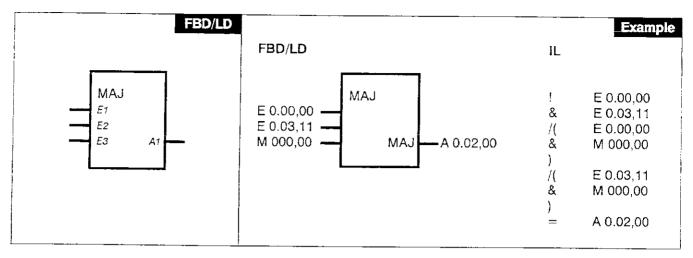

| MAJ                      | Majority                      | 63                                    |

| =                        | Allocation, binary            | 25                                    |

| Latch functions          |                               |                                       |

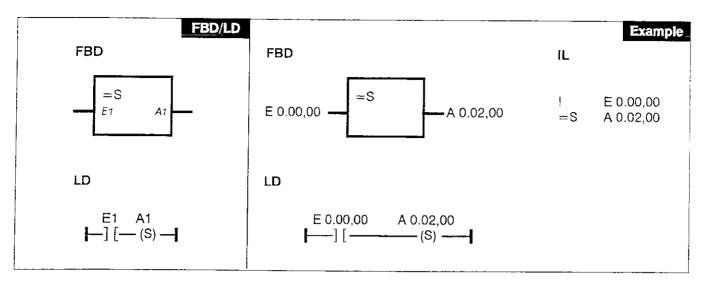

| =S                       | Allocation set type           | 30                                    |

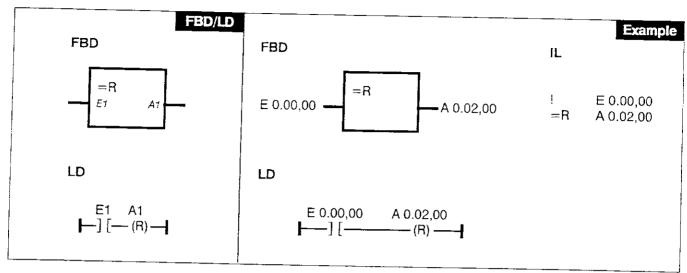

| =R                       | Allocation reset type         | 29                                    |

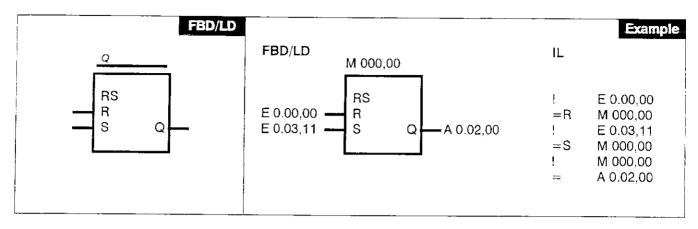

| RS                       | Dominant set latch            | 79                                    |

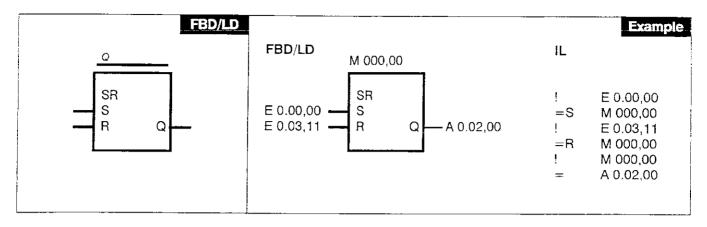

| SR                       | Dominant reset latch          | 90                                    |

| Arithmetic functions, we | ord                           |                                       |

| +                        | Addition, word                | 11                                    |

|                          | Subraction, word              | 13                                    |

| *                        | Multiplication, word          | 8                                     |

|                          | Division, word                | 16                                    |

| *:                       | Multiplier with divider       | 9                                     |

| BET                      | Absolute value, conditional   | 47                                    |

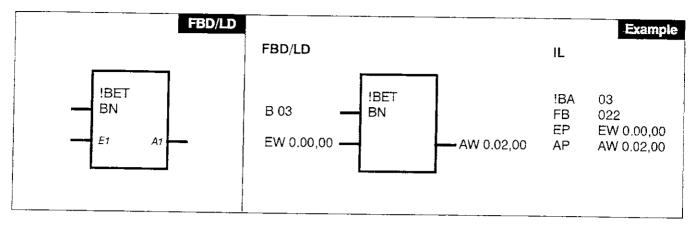

| !BET                     | Absolute value, unconditional | 3                                     |

| Call name in FBD/LD                                       | Connection element                 | Page in CE-library |

|-----------------------------------------------------------|------------------------------------|--------------------|

| Arithmetic functions, w                                   | ord                                |                    |

| KPL                                                       | Complement, conditional            | 60                 |

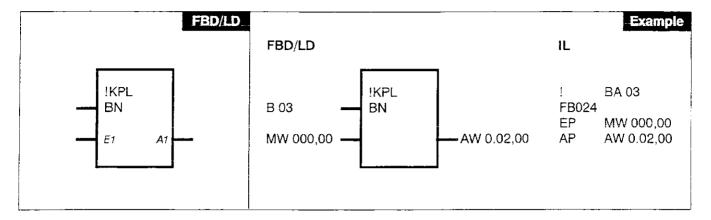

| !KPL                                                      | Complement, unconditional          | 6                  |

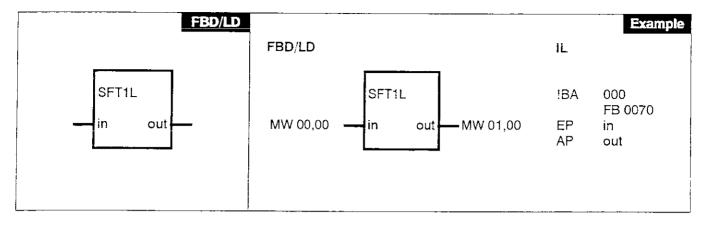

| SFT1L                                                     | Shift for 1 bit position to left   | 80                 |

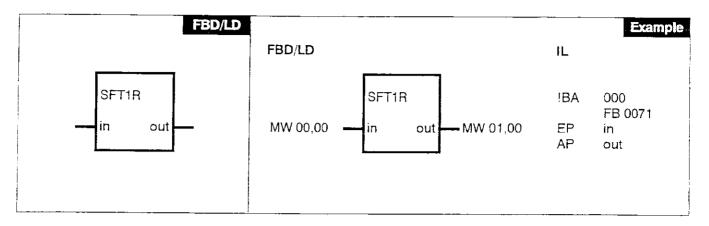

| SFT1R                                                     | Shift for 1 bit position right     | 81                 |

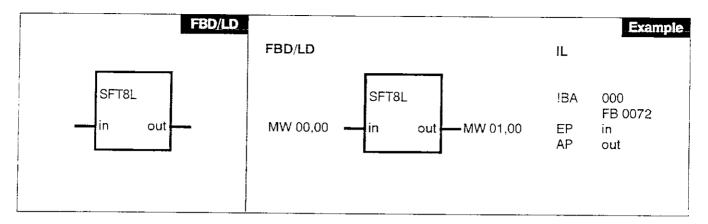

| SFT8L                                                     | Shift for 8 bit positions to left  | 82                 |

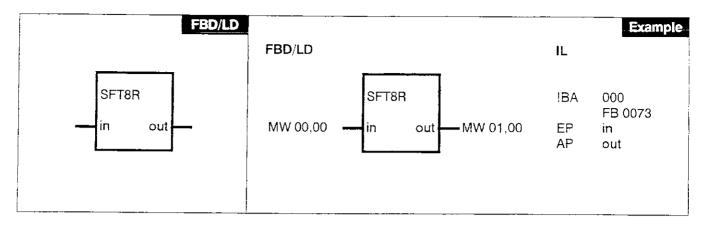

| SFT8R                                                     | Shift for 8 bit positions to right | 83                 |

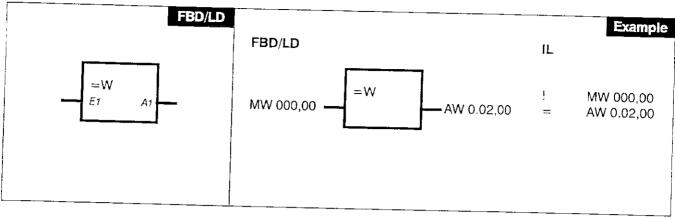

| =W                                                        | Allocation word                    | 31                 |

| Arithmetic functions, do                                  | ouble word                         |                    |

| +D                                                        | Double word addition               | 12                 |

| -D                                                        | Double word subtraction            | 14                 |

| *D                                                        | Double word multiplication         | 10                 |

| :D                                                        | Double word division               | 20                 |

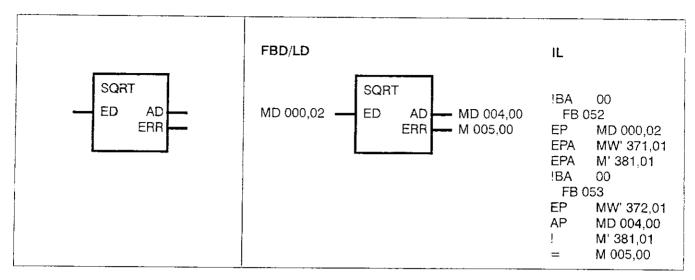

| SQRT                                                      | Square root                        | 89                 |

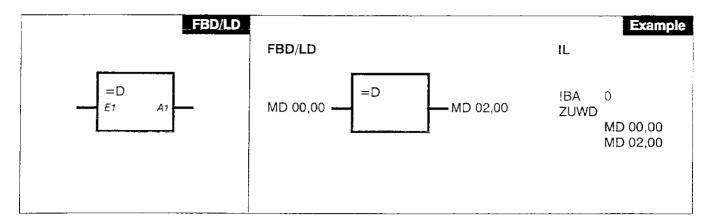

| =D                                                        | Allocation, double word            | 28                 |

| Comparison functions                                      |                                    |                    |

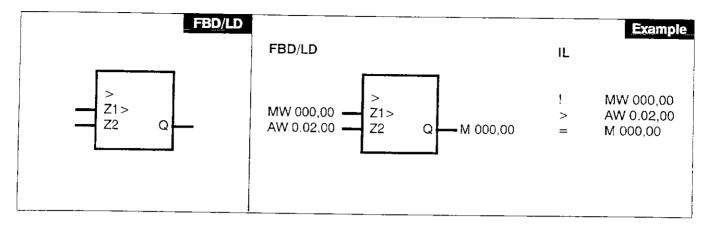

| >                                                         | Greater than, word                 | 32                 |

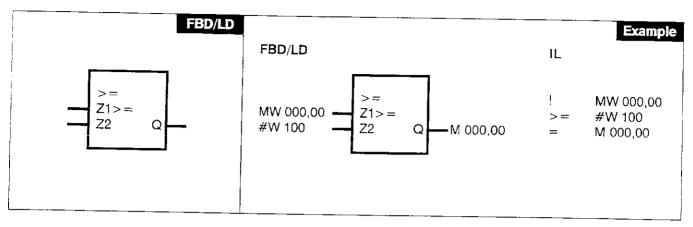

| >=                                                        | Greater than or equal to, word     | 33                 |

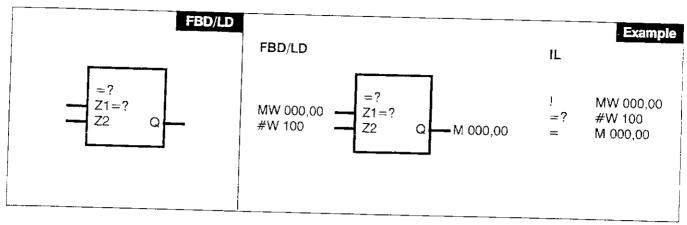

| =?                                                        | Equal, word                        | 27                 |

| <>                                                        | Not equal, word                    | 23                 |

| <=                                                        | Less than or equal, word           | 22                 |

| <                                                         | Less than, word                    | 21                 |

| >D                                                        | Greater than, double word          | 34                 |

| <d< td=""><td>Less than, double word</td><td>24</td></d<> | Less than, double word             | 24                 |

907 PC 332/Issued: 08.94 0-3

| Call name in FBD/LD      | Connection element                                         | Page in CE-library |  |

|--------------------------|------------------------------------------------------------|--------------------|--|

| Timer functions          |                                                            |                    |  |

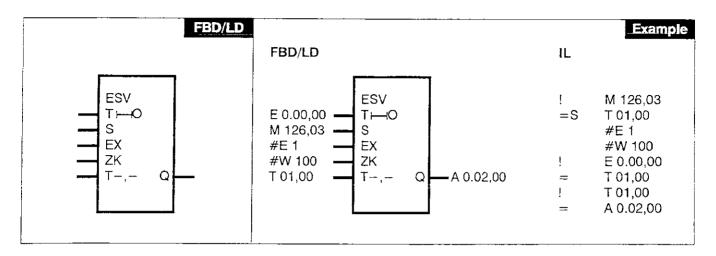

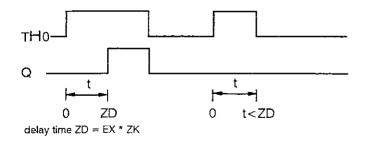

| ESV                      | On delay timer                                             | 52                 |  |

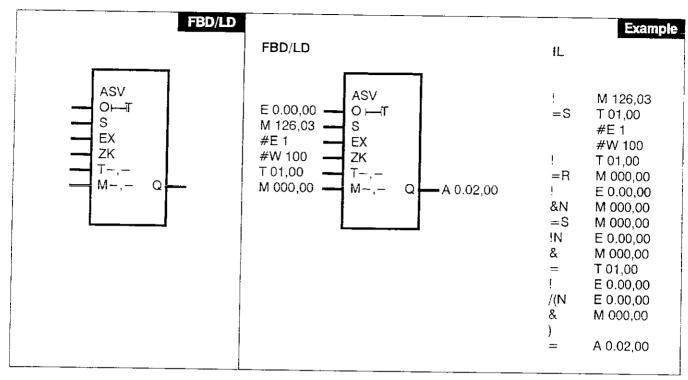

| ASV                      | Off delay timer                                            | 41                 |  |

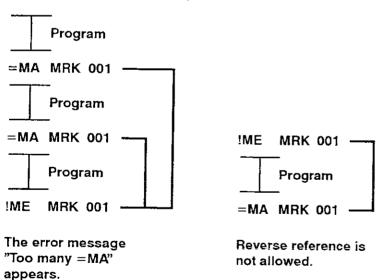

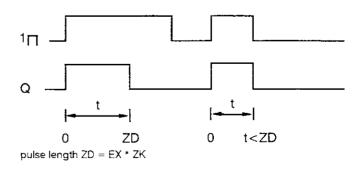

| MOA                      | Single shot timer with abortion                            | 66                 |  |

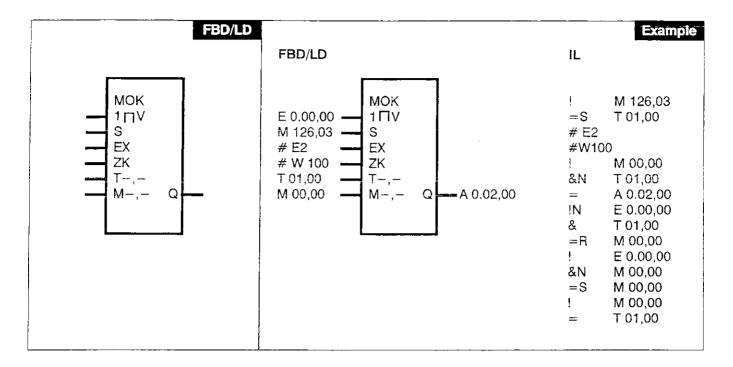

| MOK                      | Single shot timer, constant                                | 68                 |  |

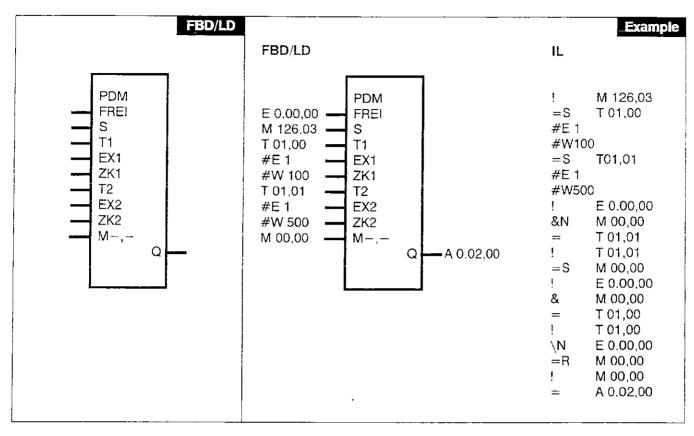

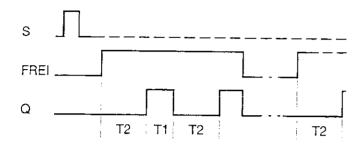

| PDM                      | Oscillator with 2 timers                                   | 76                 |  |

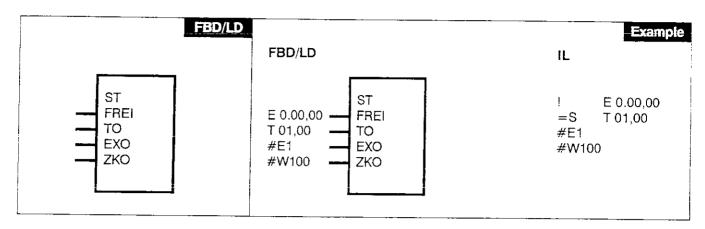

| ST                       | Timer setup value allocation                               | 91                 |  |

| Counter functions        |                                                            |                    |  |

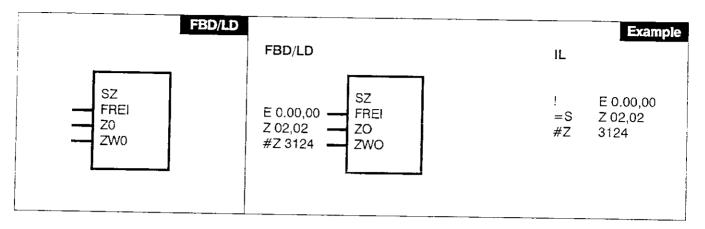

| SZ                       | Counter setup value allocation                             | 93                 |  |

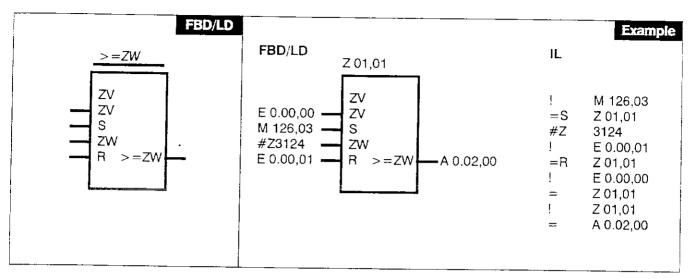

| ZV                       | Up counter                                                 | 111                |  |

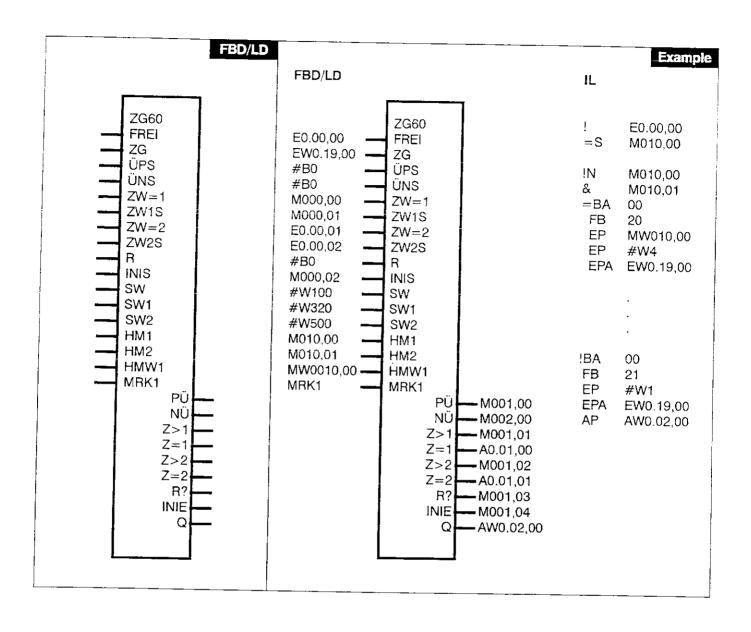

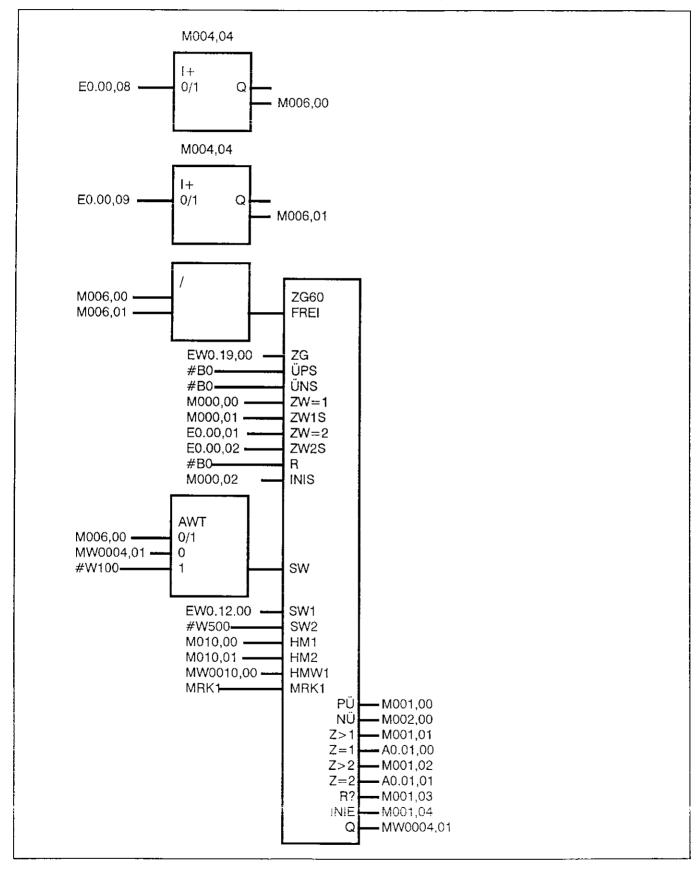

| ZG60                     | Control 07 ZG 60                                           | 107                |  |

| Program control function | ons                                                        |                    |  |

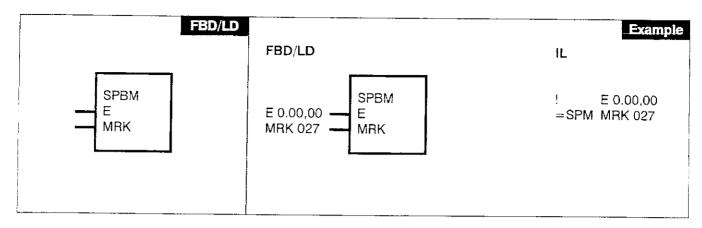

| SPBM                     | Conditional jump to label                                  | 87                 |  |

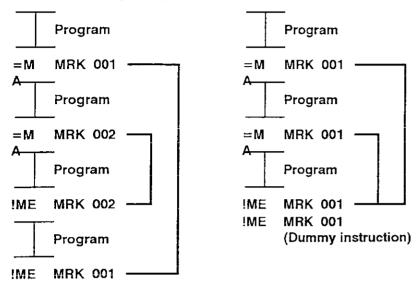

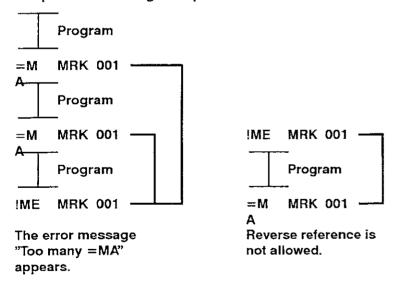

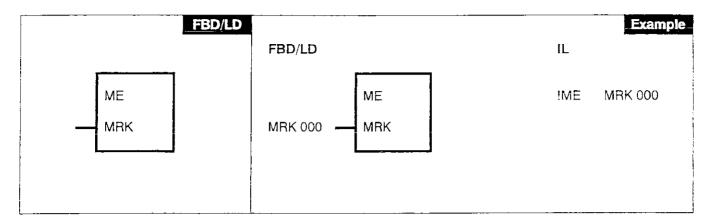

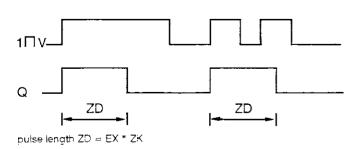

| MRK                      | Jump label                                                 | 70                 |  |

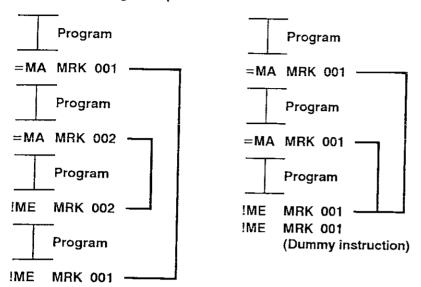

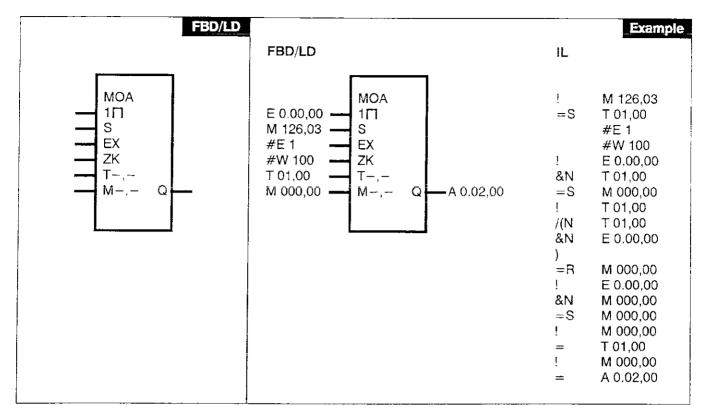

| MA                       | Label, start                                               | 61                 |  |

| ME                       | Label, end                                                 | 64                 |  |

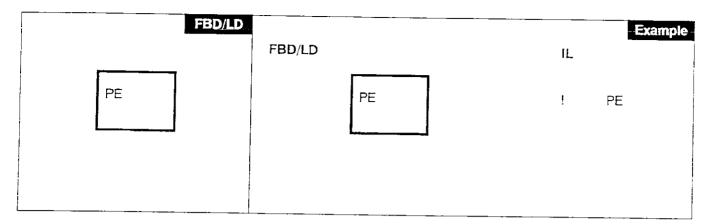

| PE                       | Program end                                                | 78                 |  |

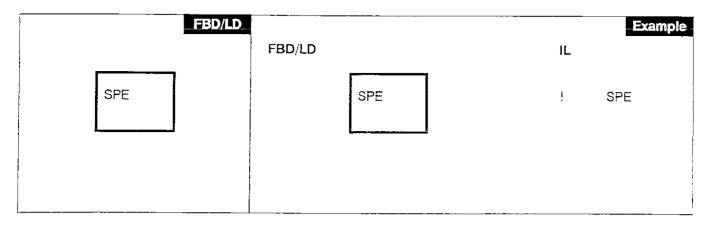

| SPE                      | Absolute end of user program                               | 88                 |  |

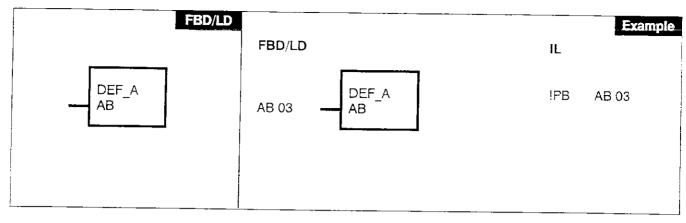

| DEF_A                    | Beginning of user function block defi-<br>nition           | 51                 |  |

| BE                       | End of user function block definition                      | 45                 |  |

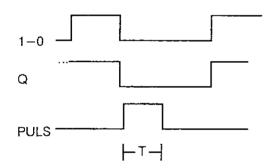

| IBE                      | End of interrupt block                                     | 56                 |  |

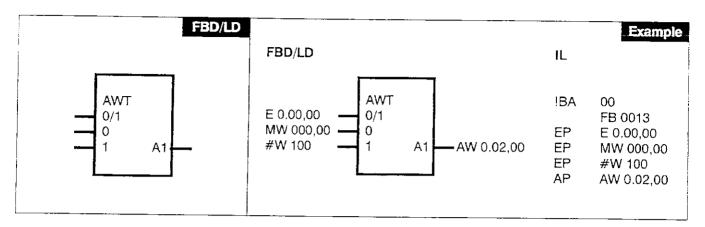

| BA_NP                    | User function block call without parameters                | 44                 |  |

| !BA_NP                   | User function block call without parameters, unconditional | 1                  |  |

| Call name in FBD/LD     | Connection element                     | Page in CE-library |

|-------------------------|----------------------------------------|--------------------|

| Format conversion       |                                        |                    |

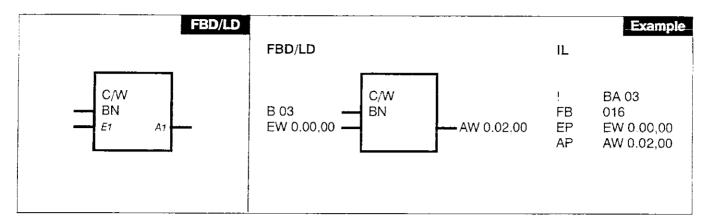

| C/W                     | BCD to binary conversion               | 48                 |

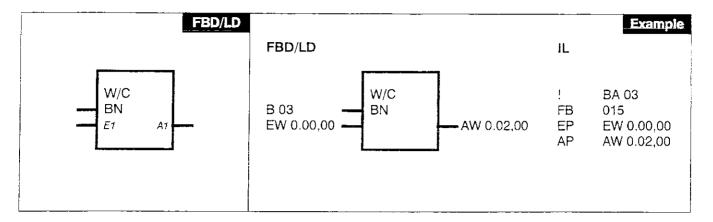

| W/C                     | Binary to BCD conversion               | 102                |

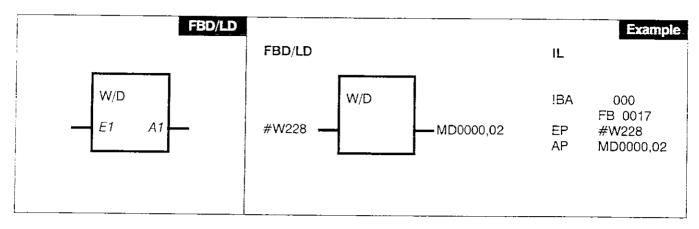

| W/D                     | Word to double word conversion         | 103                |

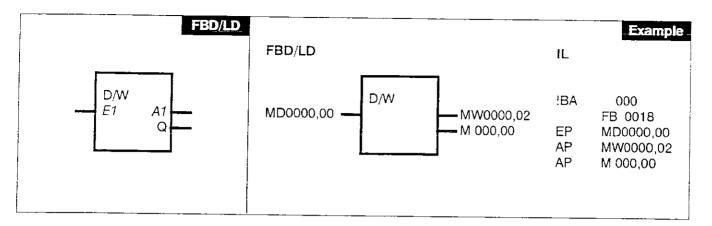

| D/W                     | Double word to word conversion         | 50                 |

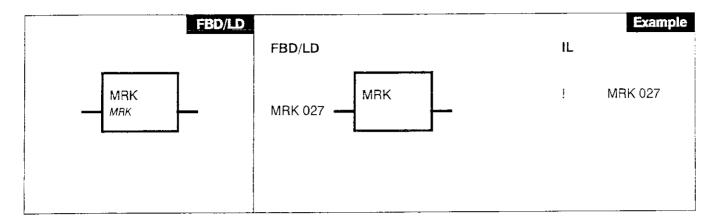

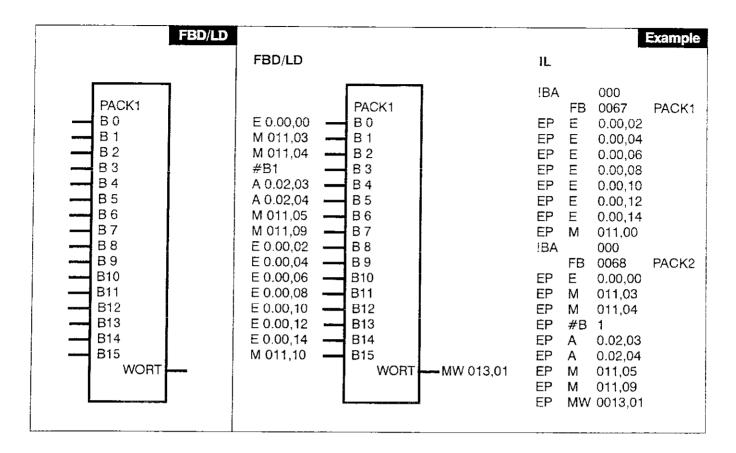

| PACK                    | Pack binary variables in word          | 72                 |

| PACK1                   | Pack word (function block)             | 74                 |

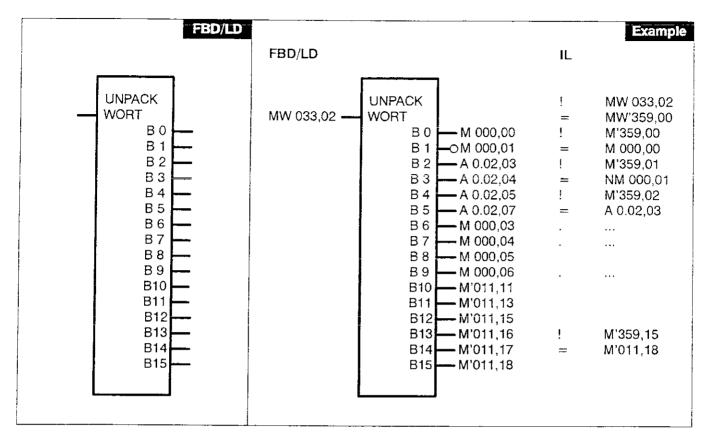

| UNPACK                  | Unpacking a word into binary variables | 98                 |

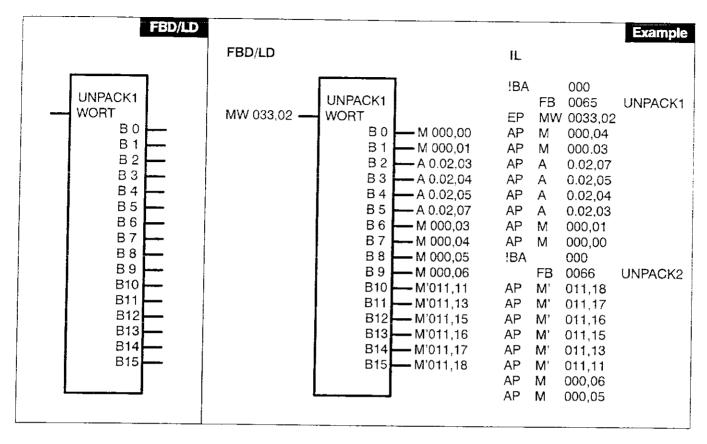

| UNPACK1                 | Unpacking a word (function block)      | 100                |

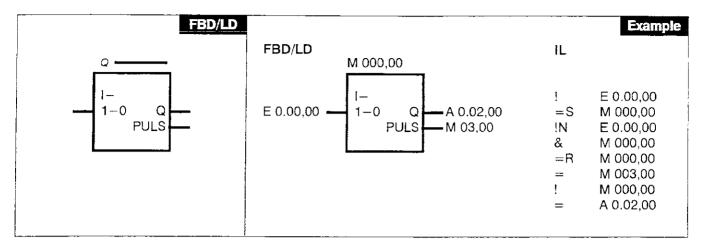

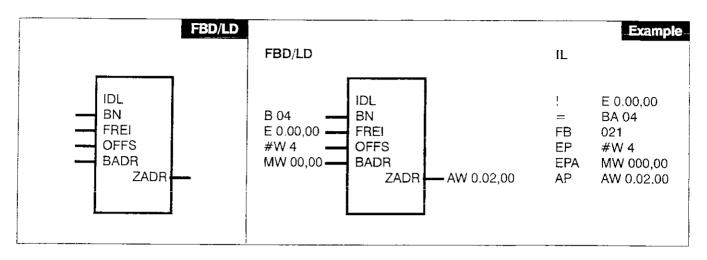

| Pulse                   |                                        |                    |

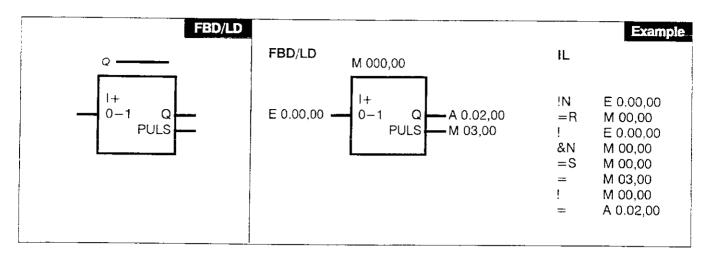

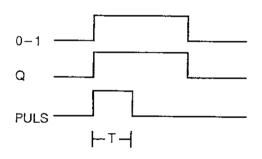

| 1+                      | Rising edge pulse                      | 53                 |

| -                       | Falling edge pulse                     | 54                 |

| Logic functions with wo | rd values                              |                    |

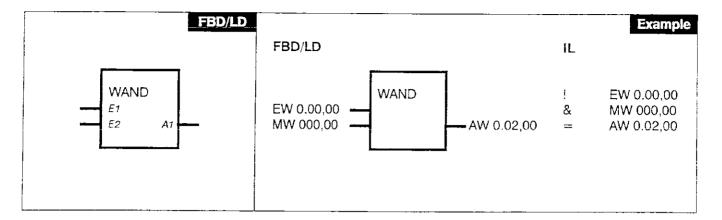

| WAND                    | Logic AND function, word               | 104                |

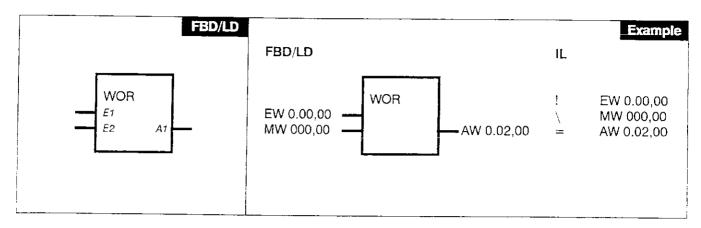

| WOR                     | Logic OR function, word                | 105                |

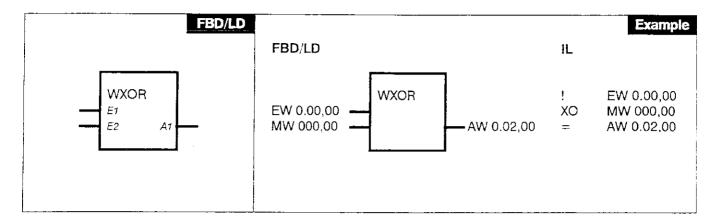

| WXOR                    | Exclusive OR logic function, word      | 106                |

| Step chains             |                                        |                    |

| ISCH                    | Initialization                         | 59                 |

| Analog value processing | 3                                      |                    |

| ANAI                    | Read analog values (07 EA 6063) 35     |                    |

| ANAI1                   | Read analog values (07 EA 6065) 37     |                    |

| ANAO                    | Output of analog values 39             |                    |

| Call name in FBD/LD    | Connection element              | Page in CE-library |

|------------------------|---------------------------------|--------------------|

| Special functions      |                                 |                    |

|                        | If then                         | 17                 |

|                        | If then, word                   | 19                 |

|                        | if then, double word            | 18                 |

|                        | NOTBIT                          | 71                 |

| Higher Order functions |                                 |                    |

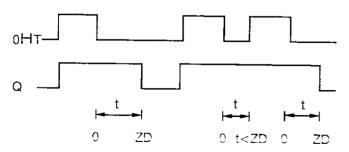

| AWT                    | Selection gate                  | 43                 |

| BEG                    | Limiter, conditional            | 46                 |

| !BEG                   | Limiter, unconditional          | 2                  |

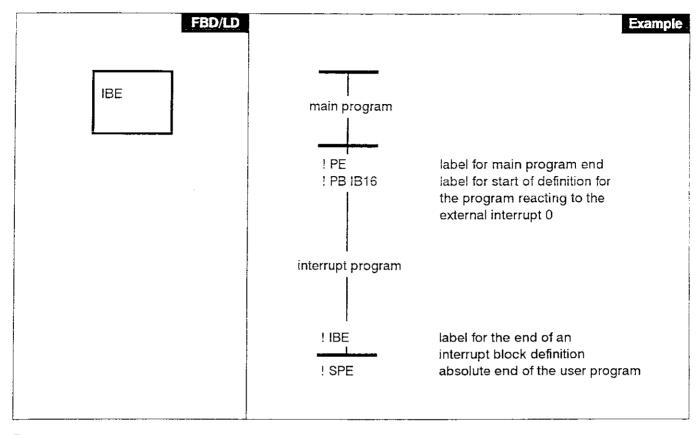

| IDL                    | Indirect reading, conditional   | 57                 |

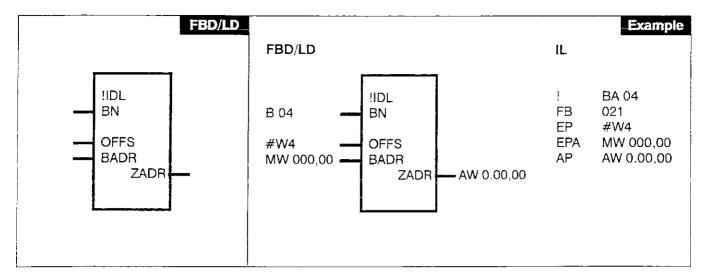

| !IDL                   | Indirect reading, unconditional | 4                  |

| IDS                    | Indirect writing, conditional   | 58                 |

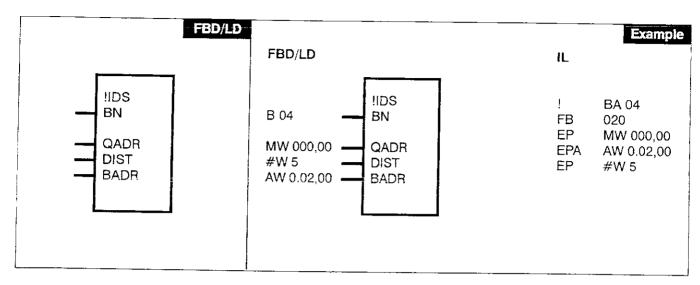

| IIDS                   | Indirect writing, unconditional | 5                  |

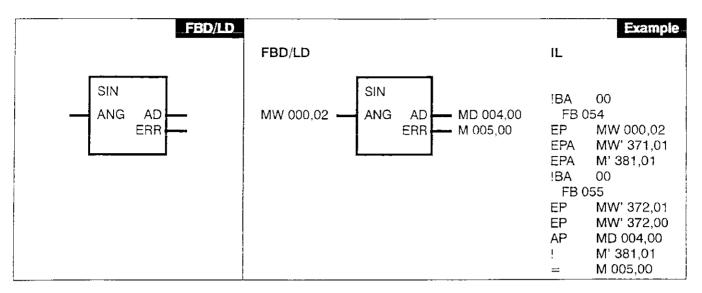

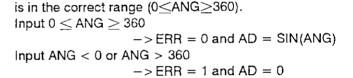

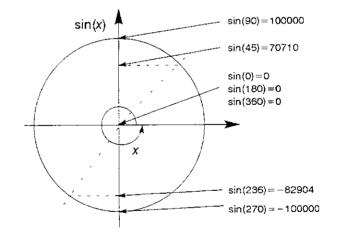

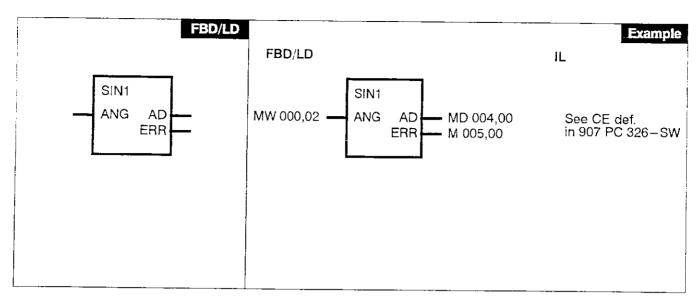

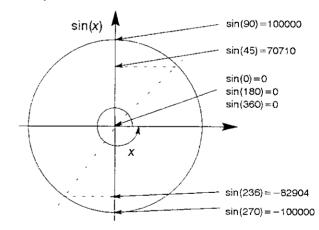

| SIN                    | Sine 0 to 360 degree            | 84                 |

| SIN1                   | Sine 0,0 to 360,0 degree        | 85                 |

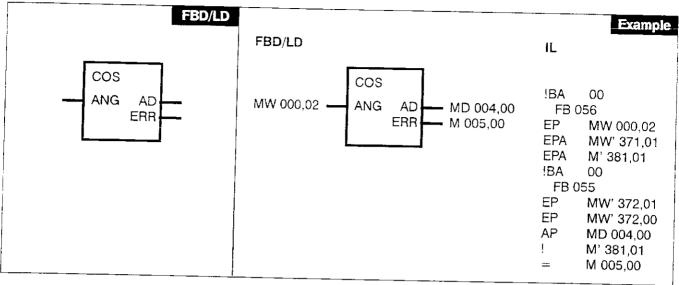

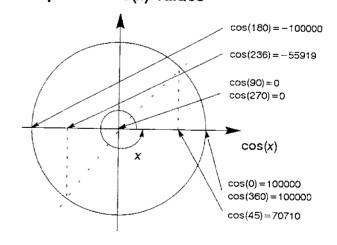

| COS                    | Cosine                          | 49                 |

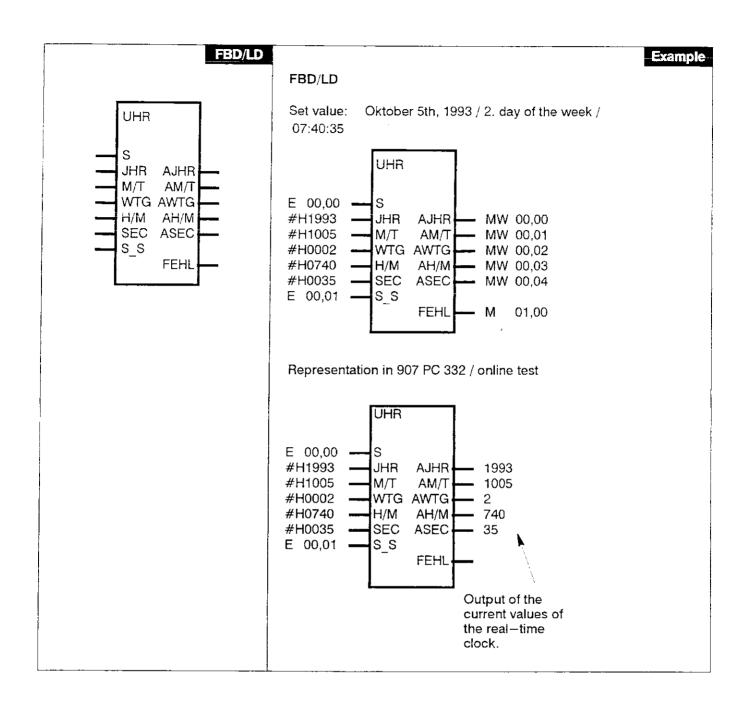

| UHR                    | Clock                           | 95                 |

# ABB Procontic T 200 functions, arranged alphabetically according to call names

The following overview summarizes the connection elements in the same order you can find them in the programming software. You will find a detailed description of the according connection element under the stated page.

| Call name in FBD/LD                                       | Connection element                                         | Page in CE-library |

|-----------------------------------------------------------|------------------------------------------------------------|--------------------|

| !BA_NP                                                    | User function block call without parameters, unconditional | 1                  |

| BEG                                                       | Limiter, unconditional                                     | 2                  |

| !BET                                                      | Absolute value, unconditional                              | 3                  |

| !IDL                                                      | Indirect reading, unconditional                            | 4                  |

| !IDS                                                      | Indirect writing, unconditional                            | 5                  |

| !KPL                                                      | Complement, unconditional                                  | 6                  |

| &                                                         | AND                                                        | 7                  |

| *                                                         | Multiplication, word                                       | 8                  |

| *:                                                        | Multiplier with divider                                    | 9                  |

| *D                                                        | Double word multiplication                                 | 10                 |

| +                                                         | Addition, word                                             | 11                 |

| +D                                                        | Double word addition                                       | 12                 |

| _                                                         | Subraction, word                                           | 13                 |

| -D                                                        | Double word subtraction                                    | 14                 |

| 1                                                         | Logic or, binary                                           | 15                 |

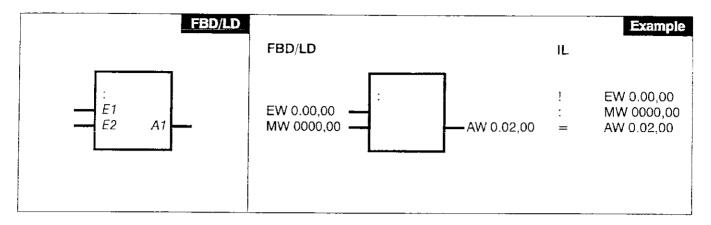

| :                                                         | Division, word                                             | 16                 |

|                                                           | If then                                                    | 17                 |

|                                                           | If then, double word                                       | 18                 |

|                                                           | If then, word                                              | 19                 |

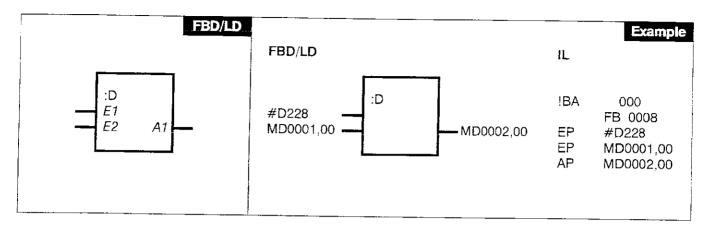

| :D                                                        | Double word division                                       | 20                 |

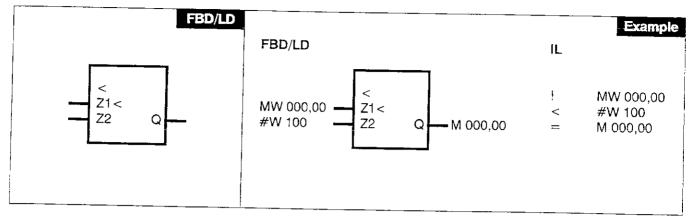

| <                                                         | Less than, word                                            | 21                 |

| <=                                                        | Less than or equal, word                                   | 22                 |

| <>                                                        | Not equal, word                                            | 23                 |

| <d< td=""><td>Less than, double word</td><td>24</td></d<> | Less than, double word                                     | 24                 |

| Call name in FBD/LD | Connection element                               | Page in CE-library |

|---------------------|--------------------------------------------------|--------------------|

| page.               | Allocation, binary                               | 25                 |

| =1                  | Exclusive or, binary                             | 26                 |

| =?                  | Equal,word                                       | 27                 |

| =D                  | Allocation, double word                          | 28                 |

| =R                  | Allocation reset type                            | 29                 |

| =S                  | Allocation set type                              | 30                 |

| =W                  | Allocation word                                  | 31                 |

| >                   | Greater than, word                               | 32                 |

| >=                  | Greater than or equal to, word                   | 33                 |

| >D                  | Greater than, double word                        | 34                 |

| ANAI                | Read analog values (07 EA 6063)                  | 35                 |

| ANAI1               | Read analog values (07 EA 6065)                  | 37                 |

| ANAO                | Output of analog values                          | 39                 |

| ASV                 | Off delay timer                                  | 41                 |

| AWT                 | Selection gate                                   | 43                 |

| BA_NP               | User function block call without parameters      | 44                 |

| BE                  | End of user function block definition            | 45                 |

| BEG                 | Limiter                                          | 46                 |

| BET                 | Absolute value                                   | 47                 |

| C/W                 | BCD to word conversion                           | 48                 |

| cos                 | Cosine                                           | 49                 |

| D/W                 | Double word to word conversion                   | 50                 |

| DEF_A               | Beginning of user function block defi-<br>nition | 51                 |

| Call name in FBD/LD                          | Connection element              | Page in CE-library |

|----------------------------------------------|---------------------------------|--------------------|

| ESV                                          | On delay timer                  | 52                 |

| 1+                                           | Rising edge pulse               | 53                 |

| <u>                                     </u> | Falling edge pulse              | 54                 |

| IBE                                          | End of interrupt block          | 56                 |

| IDL                                          | Indirect reading                | 57                 |

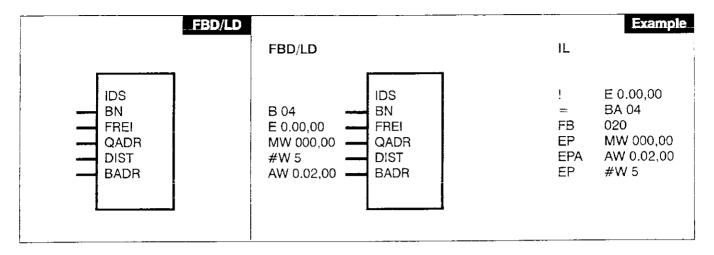

| IDS                                          | Indirect writing                | 58                 |

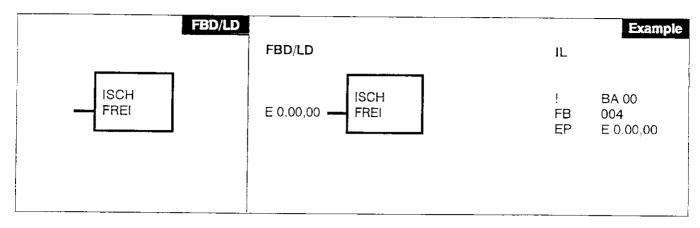

| ISCH                                         | Initialization of step chains   | 59                 |

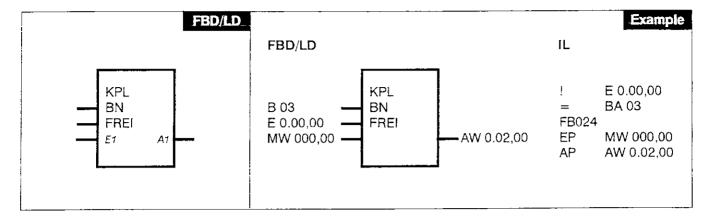

| KPL                                          | Complement                      | 60                 |

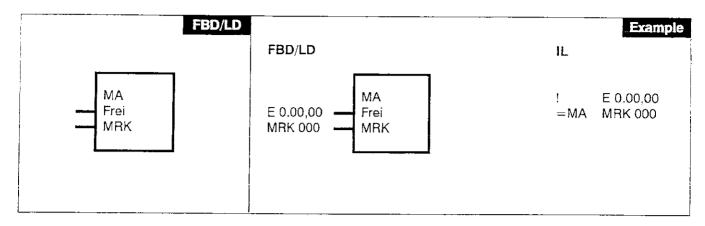

| MA                                           | Label, start                    | 61                 |

| MAJ                                          | Majority                        | 63                 |

| ME                                           | Label, end                      | 64                 |

| MOA                                          | Single shot timer with abortion | 66                 |

| MOK                                          | Single shot timer, constant     | 68                 |

| MRK                                          | Jump label                      | 70                 |

|                                              | NOTBIT                          | 71                 |

| PACK                                         | Pack binary variables in word   | 72                 |

| PACK1                                        | Pack word (function block)      | 74                 |

| PDM                                          | Oscillator with 2 timers        | 76                 |

| PE                                           | Program end                     | 78                 |

| Call name in FBD/LD Connection element |                                        | Page in CE-library |

|----------------------------------------|----------------------------------------|--------------------|

| RS                                     | Dominant set latch                     | 79                 |

| SFT1L                                  | Shift for 1 bit position to left       | 80                 |

| SFT1R                                  | Shift for 1 bit position to right      | 81                 |

| SFT8L                                  | Shift for 8 bit positions to left      | 82                 |

| SFT8R                                  | Shift for 8 bit positions to right     | 83                 |

| SIN                                    | Sine 0 to 360 degree                   | 84                 |

| SIN1                                   | Sine 0,0 to 360,0 degree               | 85                 |

| SPBM                                   | Conditional jump to label              | 87                 |

| SPE                                    | Absolute end of user program           | 88                 |

| SQRT                                   | Square root                            | 89                 |

| SR                                     | Dominant reset latch                   | 90                 |

| ST                                     | Timer setup value allocation           | 91                 |

| SZ                                     | Counter setup value allocation 93      |                    |

| UHR                                    | Clock 95                               |                    |

| UNPACK                                 | Unpacking a word into binary variables | 98                 |

| UNPACK1                                | Unpacking a word (function block)      | 100                |

| W/C                                    | Binary to BCD conversion               | 102                |

| W/D                                    | Word to double word conversion         | 103                |

| WAND                                   | Logic AND function, word               | 104                |

| WOR                                    | Logic OR function, word 105            |                    |

| WXOR                                   | Exclusive OR logic function, word 106  |                    |

| ZG60                                   | Control 07 ZG 60 107                   |                    |

| ZV                                     | Up counter                             | 111                |

0-10 907 PC 332/Issued: 08.94

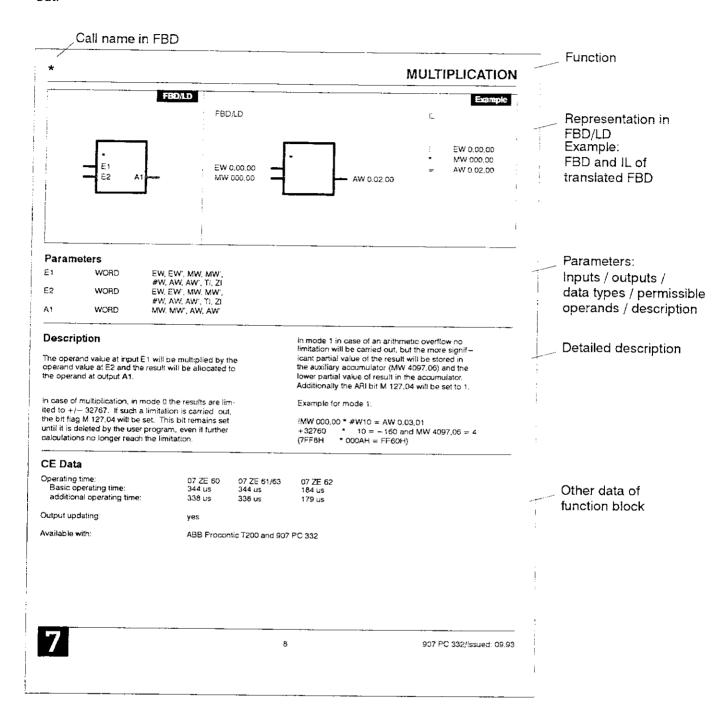

#### Instruction for use

The description of function blocks has the following layout:

## Further explanations

## FBD/LD

Input and output parameters shown in italics cannot be displayed when starting the CE.

#### Element data

Operating time:

Basic operating time: runtime without doubling Additional operating time: runtime per doubling

Output updating: specifies whether the output is re-al-

located in every cycle. In case of "no", connection to further CEs is not possible.

Note for extended IL

You can call a CE in the extended IL by using \$ < call name in the FBD> or by using the menu.

#### Display the translated IL

The translated IL of the FBD/LD or the extended IL can be displayed by using the menu (call with <space bar> -> 'Display translated IL' in the editor).

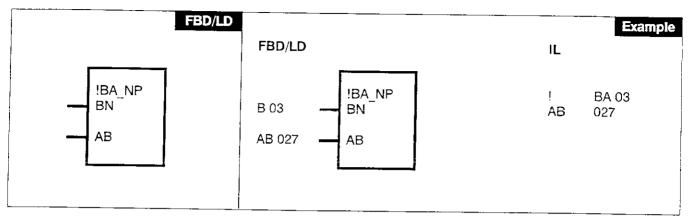

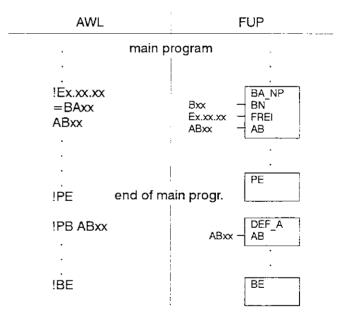

BN AB SPECIAL SPECIAL

B00 ... B255

AB00 ... AB99

Input in FBD: Bxx Input in FBD: ABxx

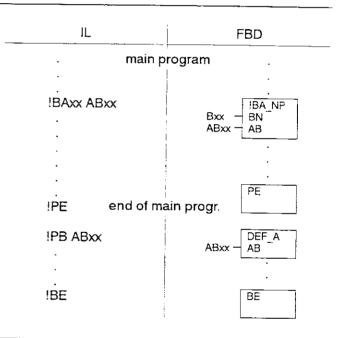

## Description

User function blocks offer the PLC user the possibility of defining, in one single step, frequently used program parts as a user block and of calling this block then as often as he wants.

The program part represented by the user function block is executed immediately after the function block is called.

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time:

33.6 μs

17.7 μs

Additional operating time:

33.6 µs

11.1 μ5

Output updating:

---

Available with:

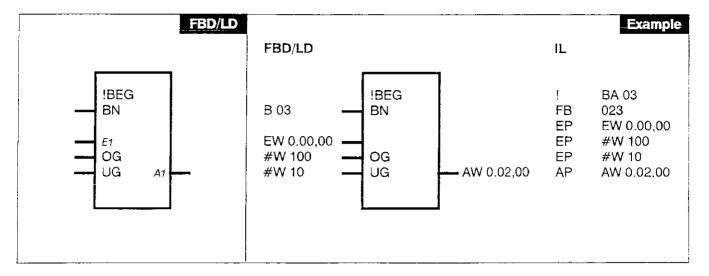

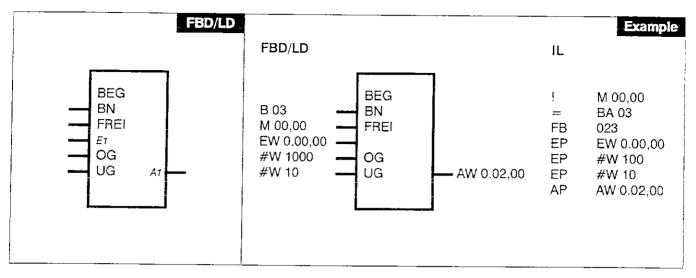

| BN | SPECIAL | B00 B255            | Input in FBD: Bxx |

|----|---------|---------------------|-------------------|

| E1 | WORD    | EW, EW', MW, MW',   | word input        |

|    |         | #W, AW, AW', TI, ZI |                   |

| OG | WORD    | EW, EW', MW, MW',   | upper limit       |

|    |         | #W, AW, AW', TI, ZI |                   |

| UG | WORD    | EW, EW', MW, MW',   | lower limit       |

|    |         | #W, AW, AW', TI, ZI |                   |

| A1 | WORD    | MW, MW', AW, AW'    | output            |

|    |         |                     |                   |

## Description

The block !BEG limits a variable input value (E1) to a maximal amplitude between adjustable limiting values (upper limit OG, lower limit UG) and allocates this limited value to an output variable (A1).

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

20.2 μs

07 ZE 62

Basic operating time: Additional operating time: 20.2 µs

11.8 us

Output updating:

yes

Memory allocated once when

called:

14 double words of 32 bit each

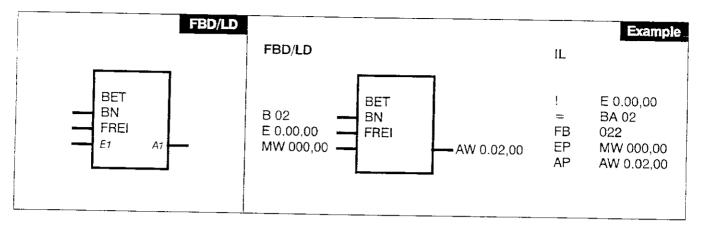

Available with:

BN **SPECIAL** E1

B 00 ... B 255 WORD

EW, EW', MW, MW',

#W, AW, AW', TI, ZI Α1 WORD

MW, MW', AW, AW'

Input in FBD: Bxx input value

amount of input value

## Description

The input variable value will be formed and will be allocated to the output variable. In other words, if the input value is negative the output value is positive. If the input value is positive the output value is also positive.

In case of -32768 (8000H) the result is again -32786, because this number is not defined.

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Additional operating time:

Basic operating time:

11.8 us

11.8 μs

5.9 µs

Output updating:

ves

Memory allocated once when

called:

5 double words of 32 bit each

Available with:

BADR

BN SPECIAL

OFFS WORD

WORD

EW, EW', MW, MW', #W, AW, AW', TI, ZI

EW, EW', MW, MW', AW, AW', TI, ZI

ZADR WORD

MW, MW', AW, AW'

Input in FBD: Bxx offset, distance

basic address

destination address

#### Description

The block transfers the variable content defined by means of the basic address and offset (distance) to the given address. Only distances values between 0 and 127 are allowed.

An allocation out of the flag ranges will not be reported.

Source address: Basic address MW 00,00

+ Offset

4

Source address MW 00,04

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time:

Additional operating time:

10.9 μs 10.9 μs

5.9 us

Output updating:

yes

\_\_\_\_

Memory allocated once when

called:

5 double words of 32 bit each

Available with:

ABB Procontic T200 and 907 PC 332

4

DIST

BN SPECIAL

QADR WORD

#W, AW, AW', Ti, Zi WORD EW, EW', MW, MW',

BADR WORD EV

#W, AW, AW', TI, ZI

EW, EW', MW, MW', AW, AW'

EW, EW', MW, MW',

Input in FBD: Bxx source address

offset

basic address

## Description

The block transfers the content of a source address to a target address, calculated from the basic address and distance. Only distance values between 0 and 127 are allowed.

Target address calculation:

for inst.: Basic address AW 0.02,00

+ Distance

5

Target address AW 0.02,05

If the calculated destination address is out of range, no allocation will be performed and the error flag M 127,04 will be set to one.

#### **CE Data**

Operating time:

07 ZE 60 20.2 μs 07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

**-υ.**-Ε μ

20.2 μs

10.1 μs

Output updating:

yes

Memory allocated once when

called:

17 double words of 32 bit each

Available with:

E1

Α1

**SPECIAL** BN

WORD

B 00 ... B 255

EW, EW', MW, MW', #W, AW, AW', TI, ZI

WORD MW, MW', AW, AW' Input in FBDs: Bxx

input value

1's complement of the input value

## Description

The block forms the 1's complement of the input variable (E1) and stores this complement in the output variable (A1).

- 1's complement: every bit is inverted separately

- · in case of bit variables the status is inverted

## **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:  $7.6 \, \mu s$

7.6 us

4.2 µs

Output updating:

yes

Memory allocated once when

called:

2 double words of 32 bit each

Available with:

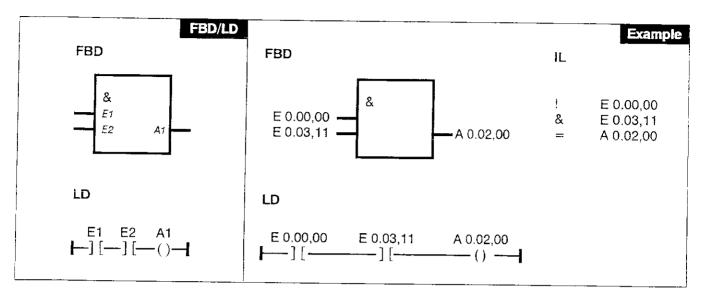

| E1 | BINARY | E, E', M, M', #B0,  | operand 1 of the AND function |

|----|--------|---------------------|-------------------------------|

|    |        | #B1, A, A', S, T, Z |                               |

E2 BINARY E, E', M, M', #B0, operand 2 of the AND function, can be duplicated #B1, A, A', S, T, Z

A1 BINARY M, M', A, A', S, T, Z result of the AND function

## Description

Logic AND function of signals at inputs E1 and E2 with result allocation to output A1.

E2 can be duplicated. The inputs and outputs can be inverted.

Truth table:

| <u>E1</u> | E2 | A1 |

|-----------|----|----|

| 0         | 0  | 0  |

| 1         | 0  | 0  |

| 0         | 1  | 0  |

| 1         | 1  | 1  |

## **CE Data**

Operating time:

07 ZE 60 07 ZE 61/63 07 ZE 62

Basic operating time:

7.9 μs 7.9 μs 6.4 μs 7.7 μs 7.7 μs 2.2 μs

Additional operating time:

Voc

Available with:

Output updating:

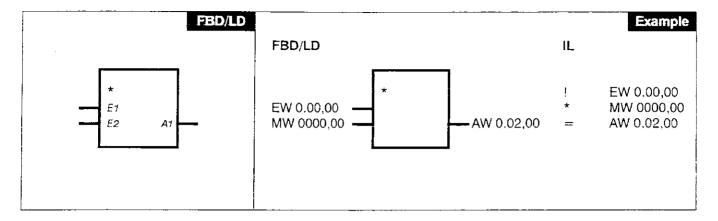

| E1 | WORD | EW, EW', MW, MW',   | Multiplicant |

|----|------|---------------------|--------------|

|    | _    | #W, AW, AW', TI, ZI |              |

| E2 | WORD | EW, EW', MW, MW',   | Multiplier   |

|    |      | #W, AW, AW', TI, ZI |              |

| A1 | WORD | MW, MW', AW, AW'    | Result       |

ABB Procontic T200 and 907 PC 332

8

#### Description

The operand value at input E1 will be multiplied by the operand value at E2 and the result will be allocated to the operand at output A1.

In case of multiplication, in mode 0 the results are limited to  $\pm 1/2 - 32767$ . If such a limitation is carried out, the bit flag M 127,04 will be set. This bit remains set until it is deleted by the user program, even if further calculations no longer reach the limitation.

In mode 1 in case of an arithmetic overflow no limitation

will be carried out, but the more significant partial value of the result will be stored in the auxiliary accumulator (MW 4097,06) and the lower partial value of the result in the accumulator. Additionally the ARI bit M 127,04 will be set to 1.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

Example for mode 1:

!MW 000,00 \* #W10 = AW 0.03,01

+32760 \* 10 = -160 and MW 4097,06 = 4

(7FF8H \* 000AH = FF60H)

#### **CE Data**

Available with:

Additional operating time:  $284 \mu s$   $284 \mu s$   $150 \mu s$

Output updating: yes

7

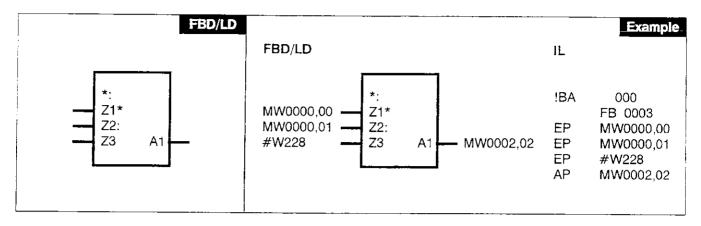

| Z1* | WORD | EW, EW', AW, AW'                        | Multiplicant |

|-----|------|-----------------------------------------|--------------|

|     | =    | MW, MW', TI, ZI, #W                     |              |

| Z2: | WORD | EW, EW', AW, AW'                        | Multiplier   |

| 70  | WORD | MW, MW', TI, ZI, #W                     | <b>8</b>     |

| Z3  | WORD | EW, EW', AW, AW'                        | Divisor      |

| A1  | WORD | MW, MW', TJ, ZI, #W<br>AW, AW', MW, MW' | Result       |

| 711 | WOND | A44, A44 , 10144, 10144                 | nesuit       |

#### Description

The value of the operand at the input Z1\* is multiplied by the value of the operand at the input Z2: , the intermediate result is divided by the value of the operand at the input Z3 and the end result is allocated to the operand at the output A1.

The end result is checked for a value transgression. The ARI BIT (M 127,04) is set for each overflow. It must be reset by the user after evaluation.

Internally, a 32-bit value is produced on multiplication so that no accuracy is lost during the course of subsequent division. The end result is rounded up if the division remainder is  $\geq$ 0.5. If a number overflow is produced (e.g. when division by 0 is performed), a value transgression is detected.

If the divisor has the value 0, the positive or negative limit value of the range of numbers is allocated to the output. For division by 0 applies:

A1 = -32767 (8001 H) if the dividend is negative and

A1 = +32767 (7FFF H) if the dividend is positive.

In both cases a value transgression is detected.

#### Range of numbers for the inputs and outputs

Integer word (16 bits).

Lower limit: 8001 H - 32 767 Upper limit: 7FFF H + 32 767 Not allowed: 8000 H ----

#### **CE Data**

Runtime:

Basic operating time:

Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 664 μs 07 ZE 61/63 664 μs

07 ZE 62 334 μs

ves

\_\_\_

92 double words of 32 bits each ABB Procontic T200 / 907 PC 332

907 PC 332/Issued: 08.94 9

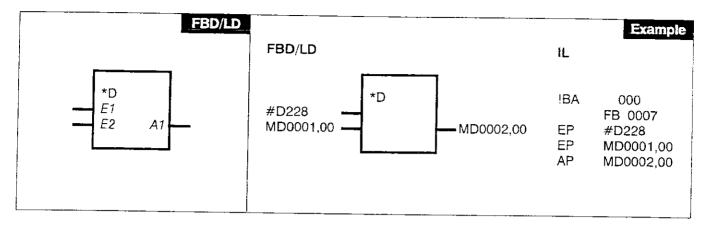

E1 DOUBLE WORD

ED, AD

E2 DOUBLE WORD

MD, MD', #D ED, AD

MD,

MD, MD', #D

DOUBLE WORD

AD. MD. MD'

Multiplicand

Multiplier

Result

## Description

Α1

The value of the double word operand at the input E1 is multiplied by the value of the double word operand at the input E2. The result is allocated to the operand at output A1.

The result is checked for a value transgression. As a function of the mode bit (M 127,15), the result is limited to  $\pm 1/2$  147483647 in the event of an overflow (mode=0) or the two flags CY (M127,00) and OV (M127,01) are set (mode=1). The ARI BIT (M 127,04) is set for each overflow. It must be reset by the user after evaluation.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers for the inputs and outputs

Integer double word (32 bits).

Lower limit:

8000 0001 H

-2 147 483 647

Upper limit:

7FFF FF**FF** H

+2 147 483 647

Not allowed: 8000 0000 H ---

## CE Data

Runtime:

Basic operating time:

Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 1166 μs 07 ZE 61/63 1166 μs 07 ZE 62 661 μs

ves

\_\_\_\_

88 double words of 32 bits each ABB Procontic T200 / 907 PC 332

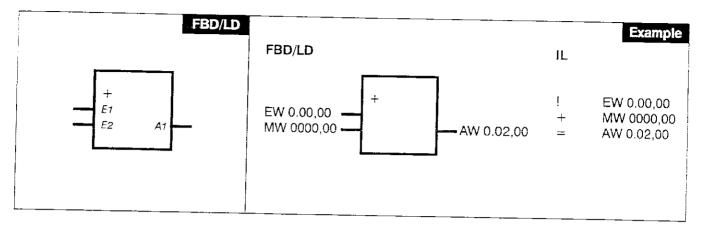

| E1 | WORD | EW, EW', MW, MW',                        | 1st summand                          |

|----|------|------------------------------------------|--------------------------------------|

| E2 | WORD | #W, AW, AW', TI, ZI<br>EW, EW', MW, MW', | 2nd summand; input can be duplicated |

| A1 | WORD | #W, AW, AW', TI, ZI<br>MW, MW', AW, AW'  | Result                               |

## Description

The operand value at input E1 will be added to the operand value at E2 and the result will be allocated to the operand at output A1.

In case of addition in mode 0 the results are limited to  $\pm 1/2$  32767. If such a limitation is carried out, the bit flag M 127,04 will be set. This bit remains set, even if further

calculations no longer reach the limitation, until it is deleted by the user program.

In mode 1 in case of an arithmetic overflow no limitation is carried out; only the Carry (M 127,00) and Overflow (M 127,01) flags will be set. The ARI bit M 127,04 is used as an additional display.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

#### Examples for mode 1:

#### Example 1:

```

!MW 000,00 + #W 10 = AW 0.03,01

+32760 + 10 = -32766 with Carry bit = 0 and Overflow bit = 1 (7FF8H) + 000AH = 8002H)

```

#### Example 2:

!MW 000,00 + #W

$$-10$$

= AW 0.03,01

-32760 +  $-10$  = +32766 with Carry bit = 1 and Overflow bit = 1

(8008H + FFF6H = 7FFEH)

#### **CE Data**

| Operating time:            | 07 ZE 60 | 07 ZE 61/63 | 07 ZE 62 |

|----------------------------|----------|-------------|----------|

| Basic operating time:      | 27.2 μs  | 27.2 us     | 16.1 µs  |

| Additional operating time: | 21.8 us  | 21.8 us     | 11.8 us  |

Output updating:

yes

Available with:

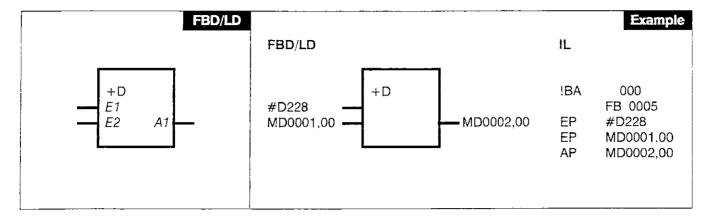

E1 DOUBLE WORD ED, AD

MD, MD', #D

E2 DOUBLE WORD

ED, AD MD, MD', #D

A1 DOUBLE WORD

AD, MD, MD'

1st summand

2nd summand

Result

#### Description

The value of the double word operand at the input E2 is added to the value of the double word operand at the input E1. The result is allocated to the operand at output A1.

The result is checked for a value transgression. As a function of the mode bit (M 127,15), the result is limited to +/-2147483647 in the event of an overflow (mode=0) or the two flags CY and OV are set (mode=1). The ARI BIT (M 127,04) is set for each overflow. It must be reset by the user after evaluation.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers

Integer double word (32 bits).

In common the following is valid:

Lower limit: 8000 0001 H Upper limit: 7FFF FFFF H

8000 0001 H -2 147 483 647 7FFF FFFF H +2 147 483 647

Not allowed: 8000 0000 H

In particular, for the inputs E1 and E2 the following is valid:

Lower limit:

8000 0000 H

-2147483648

#### CE Data

Runtime:

Basic operating time:

Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 35 μs 07 ZE 61/63 35 μs 07 ZE 62 19 μs

yes

----

25 double words of 32 bits each ABB Procontic T200 / 907 PC 332

7

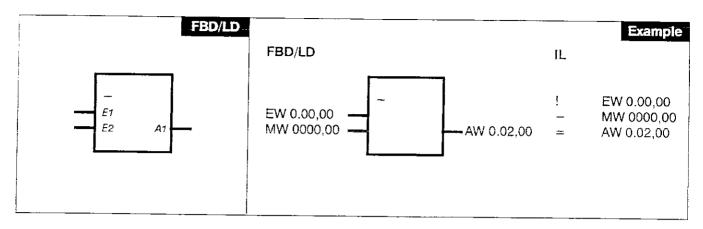

| E1 | WORD | EW, EW', MW, MW',                        | Minuend    |

|----|------|------------------------------------------|------------|

| E2 | WORD | #W, AW, AW', TI, ZI<br>EW, EW', MW, MW', | Subtrahend |

| A1 | WORD | #W, AW, AW', TI, ZI<br>MW, MW', AW, AW'  | Result     |

## Description

The operand value at input E2 will be subtracted from the value at input E1 and the result will be allocated to the operand value at A1.

In case of subtraction, in mode 0 the results are limited to  $\pm 1/2$  32767. If such a limitation is carried out, the bit flag M 127,04 will be set. This bit remains set until it is deleted

by the user program, even if further calculations no longer reach the limitation.

In mode 1 in case of an arithmetic overflow no limitation is carried out; only the Carry (M 127,00) and Overflow (M 127,01) flags will be set. The ARI bit M 127,04 is used as an additional display.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

#### Examples for mode 1:

#### Example 1:

```

!MW 000,00 - #W-10 = AW 0.03,01 +32760 - -10 = -32766 with Carry bit = 1 and Overflow bit = 0 (7FF8H - FFF6H = 8002H)

```

#### Example 2:

!MW 000,00

$$-$$

#W 10 = AW 0.03,01  $-32760$   $-$  10 =  $+32766$  with Carry bit = 0 and Overflow bit = 1 (8008H  $-$  000AH = 7FFEH)

#### **CE Data**

| Operating time:            | 07 ZE 60        | 07 ZE 61/63     | 07 ZE 62 |

|----------------------------|-----------------|-----------------|----------|

| Basic operating time:      | 28.9 μ <b>s</b> | 28.9 μ <b>s</b> | 17.0 μs  |

| Additional operating time: | 23.5 us         | 23.5 us         | 12 6 us  |

Output updating:

yes

Available with: ABB Procontic T200 and 907 PC 332

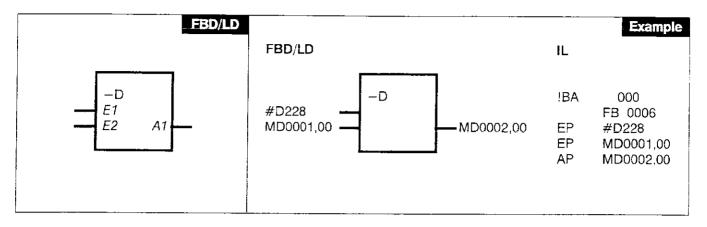

E1 DOUBLE WORD ED, AD Minuend

MD, MD', #D

E2 DOUBLE WORD ED, AD Subtrahend

MD, MD', #D

A1 DOUBLE WORD AD, MD, MD' Result

## Description

The value of the double word operand at the input E2 is subtracted from the value of the double word operand at the input E1. The result is allocated to the operand at output A1.

The result is checked for a value transgression. As a function of the mode bit (M 127,15), the result is limited to  $\pm 1/2$  147483647 in the event of an overflow (mode=0) or the two flags CY and OV are set (mode=1). The ARI BIT (M 127,04) is set for each overflow. It must be reset by the user after evaluation.

For further information on mode 0 and 1 see Section 4, Ch. 3.2.9, page 3-22.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers

integer double word (32 bits).

In common the following is valid:

Lower limit: 8000 0001 H -2 147 483 647 Upper limit: 7FFF FFFF H +2 147 483 647 Not allowed: 8000 0000 H ----

In particular, for the input E1 the following is valid:

Lower limit: 8000 0000 H -2 147 483 648

and for the input E2 the following:

Lower limit: 8000 0001 H

8000 0000 H is not allowed

#### **CE Data**

Runtime:

Basic operating time: Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 35 μs 07 ZE 61/63 35 μs 07 ZE 62 19 μs

ves

25 double words of 32 bits each ABB Procontic T200 / 907 PC 332

7

| E1 | BINARY | E, E', M, M', #B0,<br>#B1, A, A', S, T, Z    | Operand 1 of the OR function |

|----|--------|----------------------------------------------|------------------------------|

| E2 | BINARY | E, E', M, M', #B0,                           | Operand 2 of the OR function |

| A1 | BINARY | #B1, A, A', S, T, Z<br>M, M', A, A', S, T, Z | Result of the OR function    |

## Description

Logic OR function of signals at inputs E1 and E2 with result allocation to output A1.

The inputs and outputs can be inverted. The input E2 can be duplicated.

Truth table:

| E1 | E2 | A1 |

|----|----|----|

| 0  | 0  | 0  |

| 1  | 0  | 1  |

| 0  | 1  | 1  |

| 1  | 1  | 1  |

## **CE Data**

Operating time:

07 ZE 60 07 ZE 61/63 07 ZE 62

$6.4 \mu s$

Basic operating time:

7.9 μs 7.9 μs

Additional operating time:

$2.7 \,\mu s$   $2.7 \,\mu s$   $2.2 \,\mu s$

Output updating:

yes

Available with:

| E1 | WORD | EW, EW', MW, MW',   | Dividend |

|----|------|---------------------|----------|

|    |      | #W, AW, AW', TI, ZI |          |

| E2 | WORD | EW, EW', MW, MW',   | Divisor  |

|    |      | #W, AW, AW', TI, ZI |          |

| A1 | WORD | MW, MW', AW, AW'    | Result   |

|    |      |                     |          |

## Description

The operand value at input E1 will be divided by the operand value at input E2 and the result will be allocated to the operand at output A1.

The division result is the part before the comma. No rounding operation (consideration of the figures after the,

comma) will be carried out.

The ARI bit will be set when a division by 0 is carried out. In this case the accumulator is set to the positive or negative limit respectively (+32767 or -32767).

After every division you will receive the integer component in the accumulator and the remainder in the auxiliary accumulator (MW 4097,06).

#### Example for mode 1:

!MW 000,00 : #W10 = AW 0.03,01

+32761: 10 = +3276 and MW 4097,06 = 1 (remainder)

(7FF9H : 000AH = 0CCCH)

## **CE Data**

Operating time: 07 ZE 60 07 ZE 61/63 07 ZE 62 Basic operating time: 182  $\mu s$  182  $\mu s$  93  $\mu s$

Additional operating time:  $177 \mu s$   $177 \mu s$   $88 \mu s$

Output updating: yes

Available with: ABB Procontic T200 and 907 PC 332

| FBD/LD           | FBD/LD |                  | IL | Example |

|------------------|--------|------------------|----|---------|

| is not available |        | is not available |    |         |

|                  |        |                  |    |         |

## Description

IF THEN is a basic library function. The element's name in the library is :=

The element cannot be called in the CE and CE IL Editor. It can be edited in the CE IL Editor.

The programming system uses this element to realize connection lines.

## **CE Data**

Operating time:

Basic operating time:

depends on the structure

Additional operating time:

Output updating:

Available with:

| FBD/LD           |        |                   | Example |

|------------------|--------|-------------------|---------|

|                  | FBD/LD |                   | IL      |

|                  |        |                   |         |

|                  |        |                   |         |

| is not available |        | in mak ayallatılı |         |

| is not available |        | is not available  |         |

|                  |        |                   |         |

|                  |        |                   |         |

|                  |        |                   |         |

## Description

IF THEN DOUBLE WORD is a basic library function. The element's name in the library is :=DW

The element cannot be called in the CE and CE IL Editor.

The programming system uses this element to realize connection lines.

#### **CE Data**

Operating time:

Basic operating time:

depends on the structure

Additional operating time:

Output updating:

Available with:

| FBD/LD                   |        |                  | Example |

|--------------------------|--------|------------------|---------|

|                          | FBD/LD |                  | IL      |

|                          |        |                  |         |

| is not <b>a</b> vailable |        | is not available | ĺ       |

|                          |        |                  |         |

|                          |        |                  |         |

|                          |        |                  |         |

## Description

IF THEN WORD is a basic library function. The element's name in the library is := WO

The element cannot be called in the CE and CE IL Editor.

The programming system uses this element to realize connection lines.

## **CE Data**

Operating time:

Basic operating time:

depends on the structure

Additional operating time:

Output updating:

Available with:

E2

E1 DOUBLE WORD

ED, AD MD, MD', #D

DOUBLE WORD

ED, AD MD, MD', #D

A1 DOUBLE WORD

AD, MD, MD

Dividend

Divisor

Result

## Description

The value of the double word operand at the input E1 is divided by the value of the double word operand at the input E2. The result is allocated to the operand at output A1.

The result is checked for a value transgression. The ARI BIT (M 127,04) is set for each overflow. It must be reset by the user after evaluation.

If the result from the division is not an integral number, it is rounded down (e.g.: 5:3=1).

If the divisor has the value 0, the positive or negative limit value of the range of numbers is allocated to the output. For division by 0 applies:

A1 = -2 147 483 647 (8000 0001 H) if the dividend is negative and

A1 = +2 147 483 647 (7FFF FFFF H) if the dividend is positive.

In both cases a value transgression is detected.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers for the inputs and outputs

Integer double word (32 bits).

Lower limit: Upper limit:

8000 0001 H 7FFF FFFF H -2 147 483 647 +2 147 483 647

Not allowed:

8000 0000 H

\_\_\_\_

#### **CE Data**

Runtime:

Basic operating time:

Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 419 μs 07 ZE 61/63 419 us 07 ZE 62 207 μs

yes

90 double words of 32 bits each ABB Procontic T200 / 907 PC 332

| #W, AW, AW', TI, ZI  Z2 WORD EW, EW', MW, MW', comparison value  #W, AW, AW', TI, ZI  A1 BINARY M, M', A, A', S, T, Z result of the comparison | Z1< | WORD   | EW, EW', MW, MW', | value to be compared     |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|-------------------|--------------------------|

| A1 DIMADY AA A4 A A A = =                                                                                                                      | Z2  | WORD   | EW, EW', MW, MW', | comparison value         |

|                                                                                                                                                | A1  | BINARY |                   | result of the comparison |

### Description

The value of the operand at input Z1 < will be compared with the value of the operand at input Z2. If the value at Z1 < is less than the value at Z2, the state 1 will be allocated to the value of the operand at output Q, if Z1 < is equal or greater than Z1, the state 0 will be allocated to Q.

# **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

7.9 μs 7.9 μs

6.4 µs

Output updating:

yes

Available with:

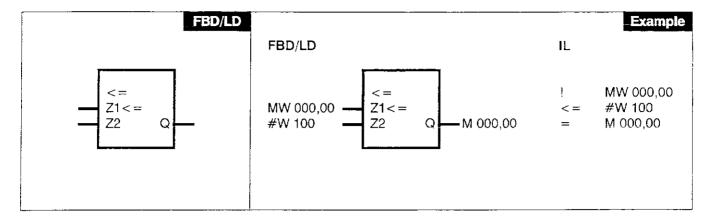

| Z1<= | WORD   | EW, EW', MW, MW',     | value to be compared     |

|------|--------|-----------------------|--------------------------|

|      | _      | #W, AW, AW', TI, ZI   |                          |

| Z2   | WORD   | EW, EW', MW, MW',     | comparison value         |

|      |        | #W, AW, AW', TI, Zi   |                          |

| A1   | BINARY | M, M', A, A', S, T, Z | result of the comparison |

|      |        |                       |                          |

### Description

The value of the operand at input Z1<= will be compared with the value of the operand at input Z2. If the value at Z1 <= is less than or equal to the value at Z2, the state 1 will be allocated to the value of the operand at output Q, if Z1 <= is greater than Z2, the state 0 will be allocated to Q.

### **CE Data**

Operating time: 07 ZE 60 07 ZE 61/63 07 ZE 62 10.3 μs 10.3 μs  $7.2 \,\mu s$ Basic operating time: \_\_\_\_

Additional operating time:

yes

Available with:

Output updating:

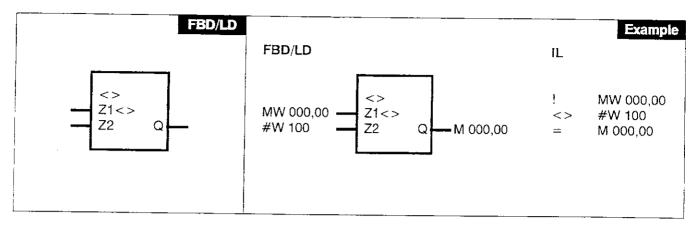

| E1 | WORD   | EW, EW', MW, MW',                            | value to be compared     |

|----|--------|----------------------------------------------|--------------------------|

| E1 | WORD   | #W, AW, AW', TI, ZI<br>EW, EW', MW, MW',     | comparison value         |

| A1 | BINARY | #W, AW, AW', TI, ZI<br>M, M', A, A', S, T, Z | result of the comparison |

### Description

The value of the operand at input Z1 <> will be compared with the value of the operand at input Z2. If the value at Z1 <> is greater or less than at Z2, the state 1 will be allocated to the value of the operand at output Q, if Z1 <> is equal Z2, the state 0 will be allocated to Q.

### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time: 7.9 µs

$7.9~\mu s$

6.4 μs

Output updating:

yes

Available with:

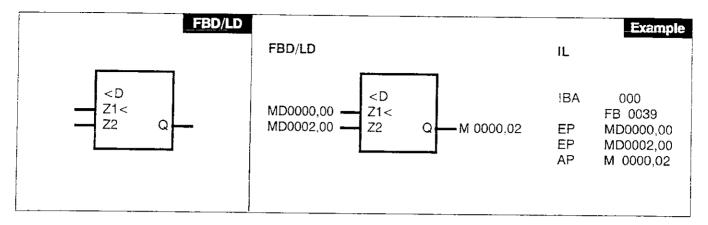

Z1 < DOUBLE WORD

ED, AD

Z2 DOUBLE WORD

MD, MD', #D ED, AD

Q BINARY

MD, MD', #D ARY A, A', M, M' value to be compared

comparison value

result of the comparison

### Description

The value of the double word operand at the input Z1 < is compared to the value of the double word operand at the input Z2.

If the value at Z1 < is less than the value at Z2, the status 1 is allocated to the value of the bit operand at the output Q, but the status 0 is allocated to Q if Z1 < is equal to or greater than Z2.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers

Integer double word (32 bits).

In common the following is valid:

Lower limit:

8000 0001 H

-2147483647

Upper limit:

7FFF FFFF H

+2 147 483 647

Not allowed: 8000 0000 H

\_\_\_\_

In particular, for the inputs Z1 < and Z2 the following is valid:

Lower limit:

8000 0000 H

-2 147 483 648

#### **CE Data**

Runtime:

Basic operating time:

Additional operating time:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 11.8 μs 07 ZE 61/63 11.8 μs 07 ZE 62 6.7 μs

yes

13 double words of 32 bits each ABB Procontic T200 / 907 PC 332

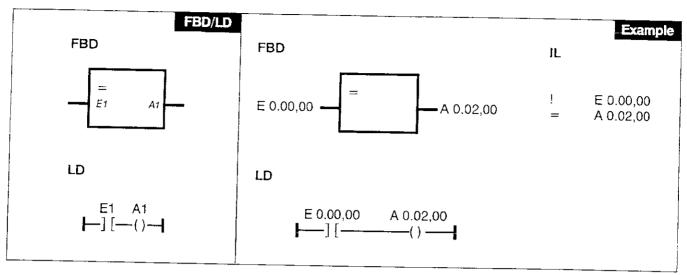

E1

A1

**BINARY**

**BINARY**

E, E', M, M', #B0,

#B1, A, A', S, T, Z

M, M', A, A', S, T, Z

source

target; output can be duplicated

# Description

The state of the operand E1 will be allocated to the operand A1.

The output A1 can be duplicated. Inputs and outputs can be inverted.

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

5.2 μs 2.5 μs 5.2 μs 2.5 μs

4.2 μs 2.0 μs

Output updating:

yes

Available with:

E1 BINARY

E, E', M, M', #B0,

operand 1 of the XOR function

E2 BINARY

#B1, A, A', S, T, Z E, E', M, M', #B0,

operand 2 of the XOR function

A1 BINARY

#B1, A, A', S, T, Z M, M', A, A', S, T, Z

result of the XOR function

### Description

Logic EXCLUSIVE OR function of signals at inputs E1 and E2 with result allocation to output A1.

#### Truth table:

| E1 | E2 | A1 |

|----|----|----|

| 0  | 0  | 0  |

| 1  | 0  | 1  |

| 0  | 1  | 1  |

| 1  | 1  | 0  |

#### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time: 7.9 μs 2.7 μs 7.9 μs 2.7 μs 6.4 μs 2.2 μs

Output updating:

yes

Available with:

| Z1=? | WORD   | EW, EW', MW, MW',                            | value to be compared     |

|------|--------|----------------------------------------------|--------------------------|

| Z2   | WORD   | #W, AW, AW', TI, ZI<br>EW, EW', MW, MW',     | comparison value         |

| Q    | BINARY | #W, AW, AW', TI, ZI<br>M, M', A, A', S, T, Z | result of the comparison |

|      |        |                                              |                          |

### Description

The value of the operand at input Z1=? will be compared with the value of the operand at input Z2. If the value at Z1=? is equal to the value at Z2, the state 1 will be allocated to the value of the operand at output Q. If Z1=? is not equal to Z2, the state 0 will be allocated to Q.

### **CE Data**

| Operating time:       |  |

|-----------------------|--|

| Basic operating time: |  |

07 ZE 60 07 ZE 61/63 07 ZE 62 e: 7.9 μs 7.9 μs 6.4 μs

Additional operating time:

Output updating: yes

Available with: ABB Procontic T200 and 907 PC 332

E1 A1 DOUBLE WORD

ED, AD, MD, MD', #D

AD, MD, MD'

Source Target

DOUBLE WORD

### Description

The value of the operand at the input E1 is allocated to the operand at the output A1.

If the inadmissible value 8000 0000 H should appear at the input for any particular reason, the permissible value 8000 0001 H  $(-2\ 147\ 483\ 647)$  will be allocated to the output A1. Therefore, the inadmissible value will be corrected.

The input and the output can neither be duplicated nonnegated.

### Number range

Integer double word (32 bits)

• Low limit:

8000 0001 H -2 147 483 647

High limit:

7FFF FFFF H + 2 147 483 647

· Inadmissible value: 8000 0000 H

#### **CE Data**

Operating time:

Basic operating time:

Additional operating time:

Output updating:

Available as of:

07 ZE 60

07 ZE 61/63

07 ZE 62

$10.8 \,\mu s$

10.8 μs

$8.7~\mu s$

ves

E1

Α1

**BINARY**

BINARY

E, E', M, M', #B0.

#B1, A, A', S, T, Z

M, M', A, A'

**RESET** input

memory variable

# Description

A logic 1-signal at input E1 sets the operand at output A1 in state 0.

. A logic 0-signal at input E1 has no influence on the operand at output A1.

#### IMPORTANT:

This CE may be used only as output CE. This means that it may not be linked further on the output side to other logic functions.

### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

$5.2 \mu s$  $2.5 \, \mu s$  5.2 µs  $2.5~\mu s$

4.2 µs  $2.0 \, \mu s$

Output updating:

Available with:

E1 BINARY

E, E', M, M', #B0,

set input

A1 BINARY

#B1, A, A', S, T, Z M, M', A, A'

memory variable

### Description

A logic 1—signal at input E1 sets the operand at output A1 in state 0.

A logic 0-signal at input E1 has no influence on the operand at output A1.

#### IMPORTANT:

This CE may be used only as output CE. This means that it may not be linked further on the output side.

#### **CE Data**

Operating time:

07 ZE 60

$2.5 \, \mu s$

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time: 5.2 μs

4.2 μs 2.0 μs

Output updating:

ves

Available with:

ABB Procontic T200 and 907 PC 332

$5.2 \mu s$

$2.5 \mu s$

E1

WORD

EW, EW', MW, MW',

input WORD

A1 WORD

#W, AW, AW', TI, ZI MW, MW', AW, AW'

output WORD

# Description

The value of the operand at input E1 will be allocated to the operand at output A1.

### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

5.4 μs

5.4 us

$2.7 \, \mu s$

4.4 μs 2.2 μs

Output updating:

yes

$2.7~\mu s$

Available with:

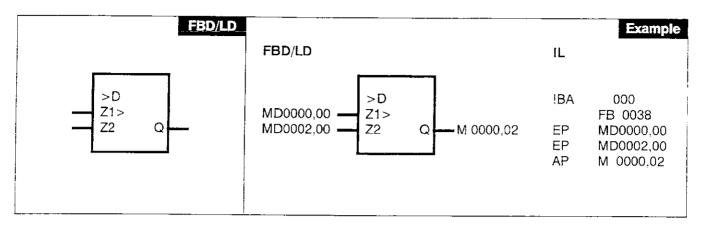

| Z1> | WORD   | EW, EW', MW, MW',<br>#W, AW, AW', TI, ZI     | value to be compared     |

|-----|--------|----------------------------------------------|--------------------------|

| Z2  | WORD   | EW, EW', MW, MW',                            | comparison value         |

| Q   | BINARY | #W, AW, AW', TI, ZI<br>M, M', A, A', S, T, Z | result of the comparison |

### Description

The value of the operand at input Z1> will be compared with the value of the operand at input Z2. If the value at Z1> is greater than at Z2, the state 1 will be allocated to the value of the operand at output Q, if Z1> is equal or less than Z2, the state 0 will be allocated to Q.

### **CE Data**

Operating time: 07 ZE 60 07 ZE 61/63 07 ZE 62 Basic operating time: 7.9  $\mu$ s 7.9  $\mu$ s 6.4  $\mu$ s

Additional operating time: --- -- ---

Output updating: yes

Available with: ABB Procontic T200 and 907 PC 332

WORD

Z1>=WORD EW, EW', MW, MW', #W, AW, AW', TI, ZI **Z**2

EW, EW', MW, MW', #W, AW, AW', TI, ZI

**BINARY** M, M, A, A, S, T, Z value to be compared

comparison value

result of the comparison

### Description

Q

The value of the operand at input Z1>= will be compared with the value of the operand at input Z2. If the value at Z1 > = is greater than or equal to the value at Z2, the state 1 will be allocated to the value of the operand at output Q, if Z1 > = is less than Z2, the state 0 will be allocated to Q.

### **CE Data**

Operating time:

07 ZE 60

07 ZE 61/63

07 ZE 62

Basic operating time: Additional operating time:

8.8 µs

$8.8 \mu s$

$6.8 \mu s$

Output updating:

ves

Available with:

Z1> DOUBLE WORD

ED, AD

Z2 DOUBLE WORD

MD, MD', #D ED, AD

DOOBLE WORD

MD, MD', #D

Q BINARY

A, A', M, M'

value to be compared

comparison value

result of the comparison

### Description

The value of the double word operand at the input Z1 > is compared to the value of the double word operand at the input Z2.

If the value at Z1 > is greater than the value at Z2, the status 1 is allocated to the value of the bit operand at the output Q, but the status 0 is allocated to Q if Z1 > is equal to or less than Z2.

Inputs and outputs can neither be duplicated nor negated.

#### Range of numbers

Integer double word (32 bits).

In common the following is valid:

Lower limit:

8000 0001 H

-2147483647

Upper limit:

7FFF FFFF H

+2 147 483 647

Not allowed: 8000 0000 H

In particular, for the inputs Z1> and Z2 the following is valid:

vanu.

Lower limit:

8000 0000 H

-2 147 483 648

### **CE Data**

Runtime:

Basic runtime:

Additional runtime:

Output updating:

Memory allocated once when called:

Available as of:

07 ZE 60 11.8 μs 07 ZE 61/63 11.8 μs 07 ZE 62 6.7 μs

ves

13 double words of 32 bits each ABB Procontic T200 / 907 PC 332

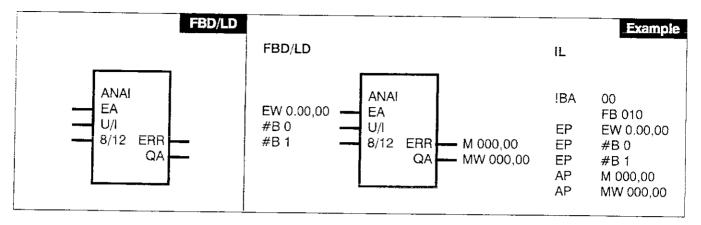

| EA   | WORD   | EW                                        | Analog input                                   |

|------|--------|-------------------------------------------|------------------------------------------------|

| U/I  | BINARY | E, E', M, M', #B0,<br>#B1, A, A', S, T, Z | Voltage/current selection                      |

| 8/12 | BINARY | E, E', M, M', #B0,<br>#B1, A, A', S, T, Z | 8/12 bits resolution selection                 |

| ERR  | BINARY | A, A', M, M'                              | Open-circuit monitoring output for 4-20 mA     |

| QA   | WORD   | MW, MW', AW, AW'                          | Analog value output in internal representation |

### Description

The ANAI block (FB 010) serves to read analog values and convert them into the internal format of  $\pm$  100 % =  $\pm$  4095 regardless of the connected analog module. In case of the modules 07 EA 61 and 07 EA 63 a broken wire is also monitored for 4...20 mA current inputs.

EA WORD Analog input

The analog input to be read is specified at the input EA.

U/I BINARY Voltage/current selection

A logic 1—signal at the binary input U/I signifies voltage input. A logic 0—signal at the binary input U/I signifies current input (see also Table 1).

8/12 BINARY 8/12 bits resolution selection

A logic 1—signal at the binary input 8/12 signifies an 8 bit input. A logic 0—signal at the binary input 8/12 signifies a 12 bit input (see also Table 1).

ERR BINARY Output, open—circuit monitoring for 4 — 20 mA

This output only works, when current input is selected (U/I = 0); applies to the 07 EA 61 and 07 EA 63 modules with current inputs of 4...20 mA).

If an open circuit is detected, the ERR output indicates a 1-signal and the QA output is set to 0.

If U/I = 1, i.e. voltage input is selected, the ERR output is always 0.

QA WORD Output, analog value in internal representation

The QA word output shows the converted value of the analog signal (internal representation).

In case of a detected open circuit the output is set to 0. The conversion of the analog signals by the ANAI block is arranged in Table 2.

| Module         | Range                                                                 | Resolution                    | U/I code                                   | 8/12 code                                |                         | <del>,</del>                                       |

|----------------|-----------------------------------------------------------------------|-------------------------------|--------------------------------------------|------------------------------------------|-------------------------|----------------------------------------------------|

| 07 EA 60       | 0 V 10 V                                                              | 8 bits                        | ——-<br>#B1                                 | #B1                                      | _                       | ANAI                                               |

| 07 EA 61       | 4 mA 20 m                                                             | A 8 bits                      | #B0                                        | #B1                                      | -                       | EA                                                 |

| 07 EA 62       | −10 V +10 V                                                           | 12 bits                       | #B1                                        | #B0                                      | <del></del>             | U/I                                                |

| 07 EA 63       | 4 mA 20 m                                                             | A 12 bits                     | #B0                                        | #B0                                      | -                       | 8/12 ERR — QA                                      |

| Table 1:       | U/I code and 8/12 c                                                   | ode of the ANAI               | function bloc                              | k                                        |                         |                                                    |

| Module<br>type | Input<br>range                                                        | ANAI, inpu<br>decimal         | t value EA<br>hexaded                      |                                          | ANAI, output<br>decimal | value QA<br>hexadecimal                            |

| 07 EA 60       | 0 V 10 V                                                              | 0 255                         | 5 0000 <sub>н</sub> .                      | OOFF <sub>H</sub>                        | 0 4080                  | 0000 <sub>H</sub> 0FF0 <sub>F</sub>                |

| 07 EA 61       | 4 mA 20 m<br>< 3.6 mA                                                 | A 8 255<br>≤2                 | 5 0008 <sub>H</sub><br>≤ 0002 <sub>H</sub> | 00FF <sub>H</sub>                        | 0 4080<br>ERR = 1 (ope  | 0000 <sub>H</sub> 0FF0 <sub>F</sub><br>en circuit) |

| 07 EA 62       | -10 V 0 V<br>+ 0 V +10 V                                              | - 2048 1<br>+ 0 2047          | 0800 <sub>H</sub> *                        | 0FFF <sub>H</sub> *<br>07FF <sub>H</sub> | 4096 – 2<br>0 4094      | F000 <sub>H</sub> FFFE <sub>I</sub>                |

| 07 EA 63       | 4 mA 20 m.<br>< 3.75 mA                                               | A 64 4095<br>≤2               | 5 0040 <sub>H</sub><br>≤ 0002 <sub>H</sub> | . OFFF <sub>H</sub>                      | 0 4095<br>ERR = 1 (ope  | 0000 <sub>H</sub> 0FFF <sub>F</sub><br>en circuit) |

| * Here, 080    | 00 <sub>H</sub> stands for F800 <sub>H</sub> =                        | = - 2048 <sub>DEC</sub> , 0FI | FF <sub>H</sub> stands fo                  | or FFFF <sub>H</sub> = -                 | - 1 <sub>DEC</sub>      |                                                    |

| Table 2:       | Conversion of the ar<br>More detailed tables<br>the individual analog | are in the hardw              |                                            |                                          |                         |                                                    |

# **CE Data**

| Operating time:                     | 07 ZE 60     | 07 ZE 61/63        | 07 ZE 62 |

|-------------------------------------|--------------|--------------------|----------|

| Basic operating time:               |              |                    |          |

| Voltage input (07 EA 60, 07 EA 62): | 17.6 μs      | 17.6 μs            | 9.2 μs   |

| Current input (07 EA 61, 07 EA 63): | 68.0 μs      | 68.0 μs            | 36.1 μs  |

| Additional operating time:          |              |                    |          |

| Output updating:                    | yes          |                    |          |

| Memory allocated once when called:  | 131 double v | words with 32 bits | each     |

| Available with:                     | ABB Procont  | tic T200 and 907 P | C 332    |

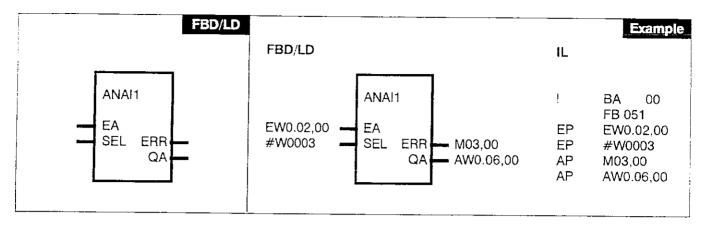

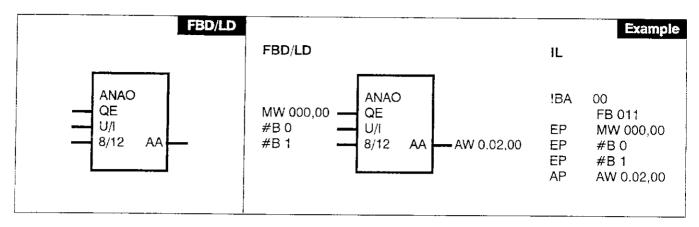

| EA<br>SEL | WORD<br>WORD | EW, EW', MW, MW'<br>EW, EW', AW, AW',<br>MW. MW' | Analog input Analog module selection                                            |

|-----------|--------------|--------------------------------------------------|---------------------------------------------------------------------------------|

| ERR       | BINARY       | A,A', M, M'                                      | Open-circuit monitoring output                                                  |

| QA        | WORD         | AW, AW', MW, MW'                                 | (only for 07 EA 61 and 07 EA 63) Analog value output in internal representation |

### Description

The ANAI1 function block (FB 051) serves to read analog values and convert them into the internal format of  $\pm$  100 % =  $\pm$  4095, regardless of the connected analog module. In case of the 07 EA 61 and 07 EA 63 modules (current inputs of 4...20 mA), the block additionally offers an open-circuit detection facility.

The ANAI1 function block is suitable for the 07 EA 60...65 analog input modules and can therefore be used as an alternative in place of the ANAI block. ANAI, however, can continued to be used for the 07 EA 60...63 modules. One separate function block is necessary for each analog input.

The function block is an element of the T200 basic library.

### EA WORD

The analog input to be read is specified at the EA input.

#### SEL WORD

The used module type is specified at the SEL input of the function block (SEL code see Table 1). If a number greater than 5 is given to the SEL input, the ERR output is set to 1 and the QA output is set to 0.

#### ERR BINARY

If an open circuit is detected, the ERR output indicates a 1-signal and the QA output is set to 0. This applies only to the 07 EA 61 and 07 EA 63 modules (with current inputs of 4...20 mA).

#### QA WORD

The QA word output shows the converted value of the analog signal (internal representation). In case of a detected open circuit the output is set to 0.

The conversion of the analog signals by the ANAI1 block is arranged in Table 2.

| Module         | Range                                                                  | Resolution                | SEL code                                   |                                          |                            |                                    |                  |

|----------------|------------------------------------------------------------------------|---------------------------|--------------------------------------------|------------------------------------------|----------------------------|------------------------------------|------------------|

| 07 EA 60       | 0 V 10 V                                                               | 8 bits                    | #W0                                        |                                          |                            |                                    |                  |